- 全部

- 默认排序

高速PCB设计指南之八

高速PCB设计指南之八第一篇掌握IC封装的特性以达到最佳EMI抑制性能将去耦电容直接放在IC封装内可以有效控制EMI并提高信号的完整性,本文从IC内部封装入手,分析EMI的来源、IC封装在EMI控制中的作用,进而提出11个有效控制EMI的设计规则,包括封装选择、引脚结构考虑、输出驱动器以及去耦电容的

如果您曾经尝试过去除设计的某个区域,您可能会发现这个过程比想象的更加复杂。如果我们使用显示元素(show element)功能来选择该区域中的铺面,就会选中整个形状。这样可能会超出到想要修改的区域之外;区域周边走线也会较为曲折。我们是否要删除整个 cline,再重新连接其他的线?是否会分段删除、减少

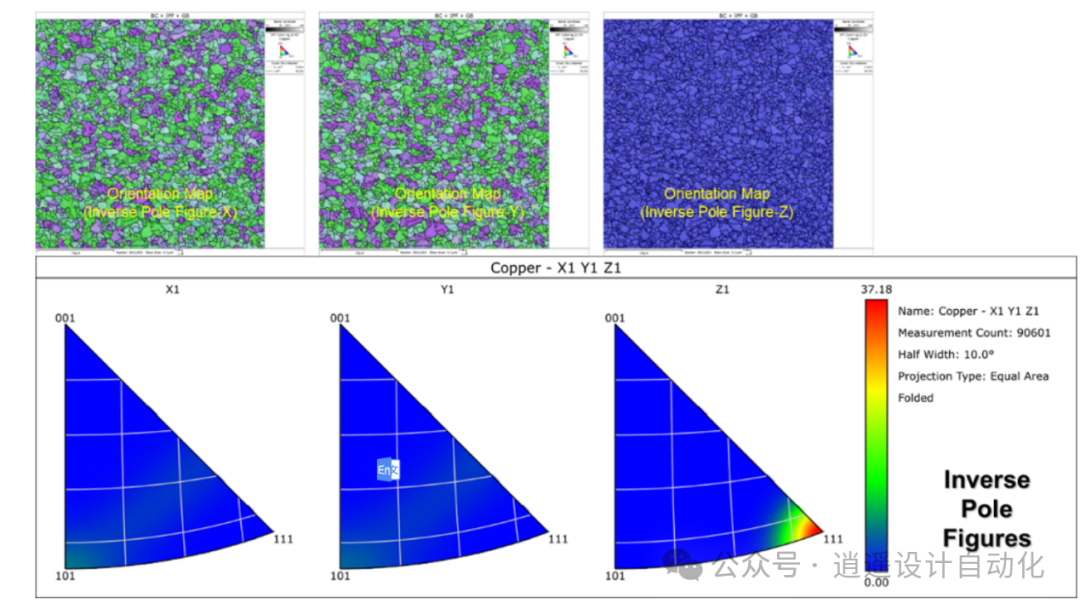

简介后摩尔时代,半导体产业面临着制程技术逼近物理极限的挑战。为实现“超越摩尔定律”的目标,2.5D/3D 封装技术加速发展。本文将探讨一种由交通大学陈智教授意外发现的革命性材料——纳米双晶铜,其在3D芯片封装中的应用及观察方法。什么是纳米双晶铜?纳米双晶铜是指铜的微观结构呈现(111)单一方向柱状晶

常见的芯片(IC)封装包括以下几种:Dual In-line Package (DIP):双列直插封装,是最早的IC封装形式之一,引脚呈“直排”式,适用于手工焊接。Quad Flat Package (QFP):四角平封装,引脚呈“平排”式

我有个元件logIC封装画错了,这个错误的元件已经放到原理图里去了。我现在到库里修改正确了元件。我的问题是怎么把这个正确的元件,从库里更新到原理图里去。@z 问问题排队

我通过region制作了异形焊盘作为IC封装的引脚,在PCB layout中使用该IC时,规则检查时报错short-circuit constraintRegion(0 holes)Top layer Pad U1-(351.132mil, 431.205mil)Top layer

扫码关注

扫码关注