- 全部

- 默认排序

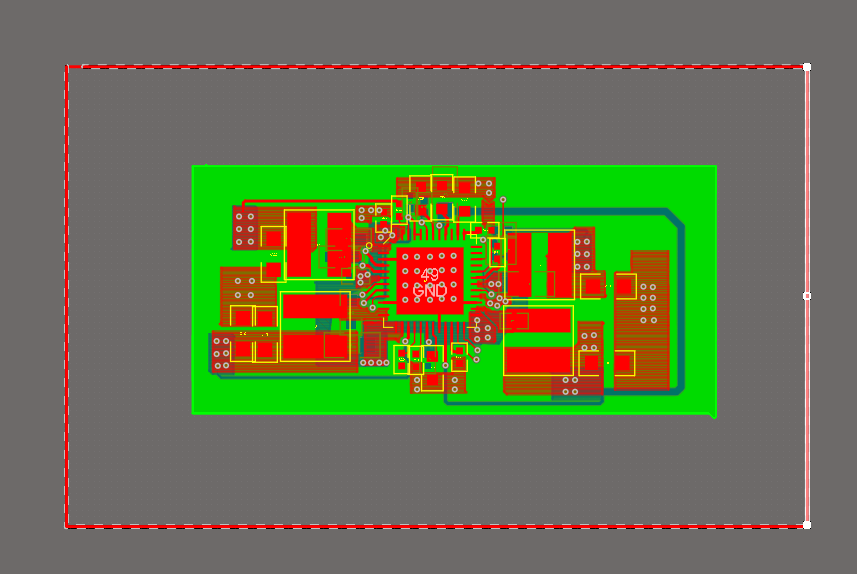

后期自己按照你画的生成板框2.存在多处DRC3.器件摆放尽量中心对齐处理4.注意铺铜尽量包裹住焊盘,这样容易造成不完全连接5.此处铜皮不满足载流,建议加宽铜皮宽度载流计算都是以最窄处计算的,后期自己修改一下6.注意电感下面尽量不要放置器件和

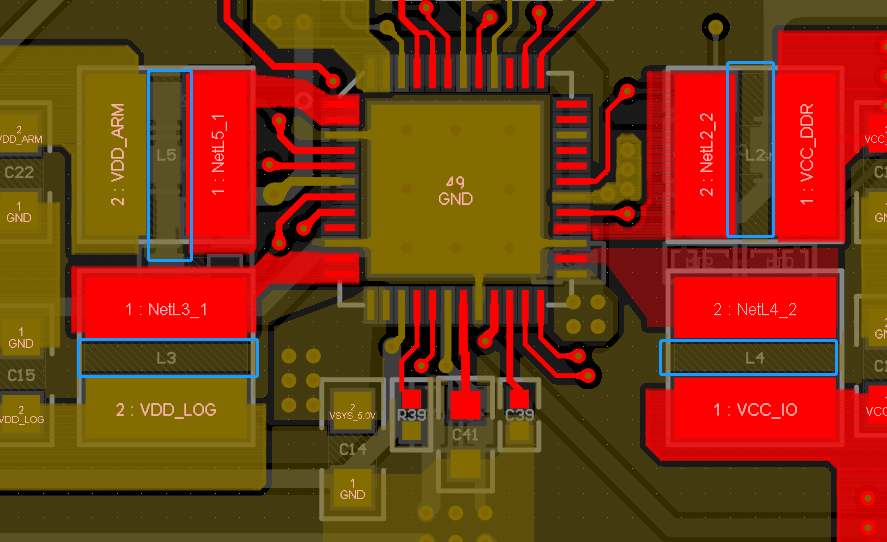

电感所在层的内部需要挖空处理2.反馈走10mil即可3.电感下面尽量不要放置器件和走线后期自己调整一下布局4.此处可能出现载流瓶颈,后期自己加宽一下铜皮宽度5.注意铜皮尽量不要出现任意角度和直角,建议45度6.存在多处DRC7.地网络不用走

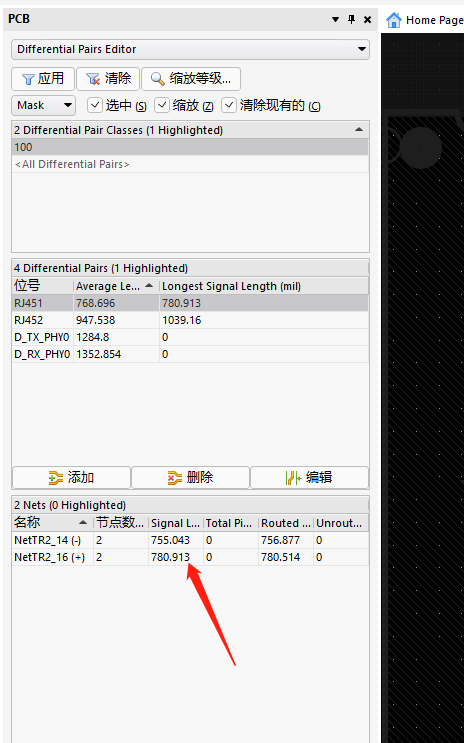

网口差分需要进行对内等长,误差5mil2.走线需要优化一下,尽量不要出现直角3.差分出线要尽量耦合4.差分焊盘出线尽量从四角出线,后期自己优化一下5.差分需要按照阻抗线宽线距走线,避免后期造成阻抗突变6.存在多处DRC7.时钟信号包地,尽量

为确保电子产品的顺利上市,集成电路(IC)不能缺少“流片阶段”,在流片前,设计规则检查(DRC)与版图与电路图一致性检查(LVS)是确保芯片成功制造并符合预期功能的关键步骤。1、电容长宽比检查确保电容长宽比合理,避免电场分布不均,影响性能。

扫码关注

扫码关注