- 全部

- 默认排序

CAN通信滤波设置

在CAN通信中,有时候我们只想接收需要的ID,而滤出掉不需要的消息,这时候我们就需要添加滤波配置,本次以STM32F103RC为例来说明,首先来看什么是有效报文01 有效报文根据CAN协议,当报文被正确接收,这里指的是直到最后一位都没有报错,且通过了标识符过滤,那么该报文被认为是有效报文,是我们需要

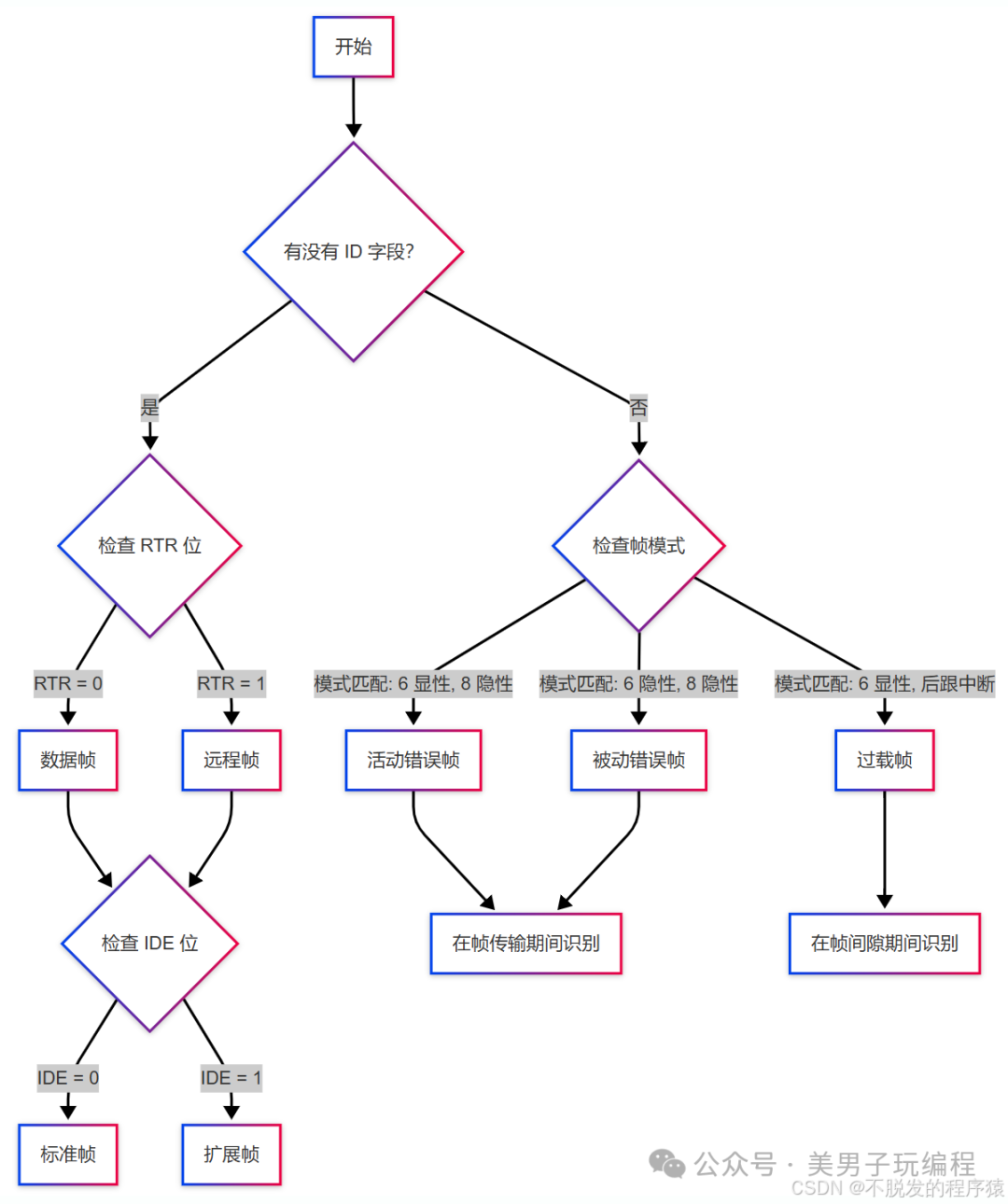

要确定 CAN 帧的类型,需要分析其结构和特定字段。以下是详细步骤: 第一步:识别是数据/远程帧还是错误/过载帧数据和远程帧:以帧开始(SOF)位开始,随后是标识符(ID)字段。错误和过载帧:没有 ID 字段,具有特定的标志和分隔符序列。第二步:区分数据帧和远程帧对于数据和远程帧,检查控制字段中的远

尤其是当系统需求变更或多个供应商协作开发时,对比 DBC 文件以找出差异和潜在问题是至关重要的。本文将深入探讨如何通过 Python 的 CANtools 库,实现高效、准确地对比多个相似的 CAN DBC 数据。CANtools 是 Python 领域中一个强大的 CAN 协议处理库,广泛用于汽车

在Ansys中的circuit仿真中,绘图的数据显示不出来是什么问题改变一下公式可以显示V(vload)-V(vn)有 [error] CANnot extract data for the trace提示 单独V(vload)就正常了

使用的软件是Cadence17.4,使用内部的allegro 3D CANavs看到的很多器件封装是完整的如下图但是无论通过allegro 3D CANavs里面的export还是直接用pcb editor里面的 export生成的stp或

扫码关注

扫码关注