- 全部

- 默认排序

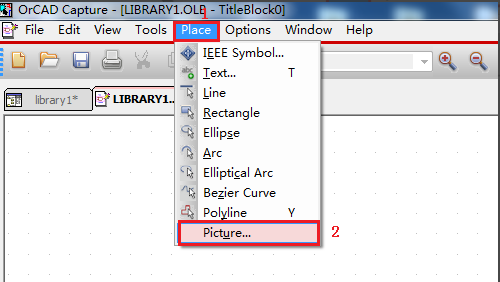

一般来说,Title Block都是调用系统本身自带的,或者是修改自带的文件,所以这里我们直接复制一个系统自带的Title Block,修改后保存在路径下,进行关联即可。 第一步,从系统自带的模板CAPsym.olb中复制一个TitleBlock0到自己创建的库的路径下,选中这个元件,按Ctrl+C进行复制,然后复制到自己创建的库路径下,如图2-33所示: 图2-33 复制系统自带库示意图第二步,将复制的Title B

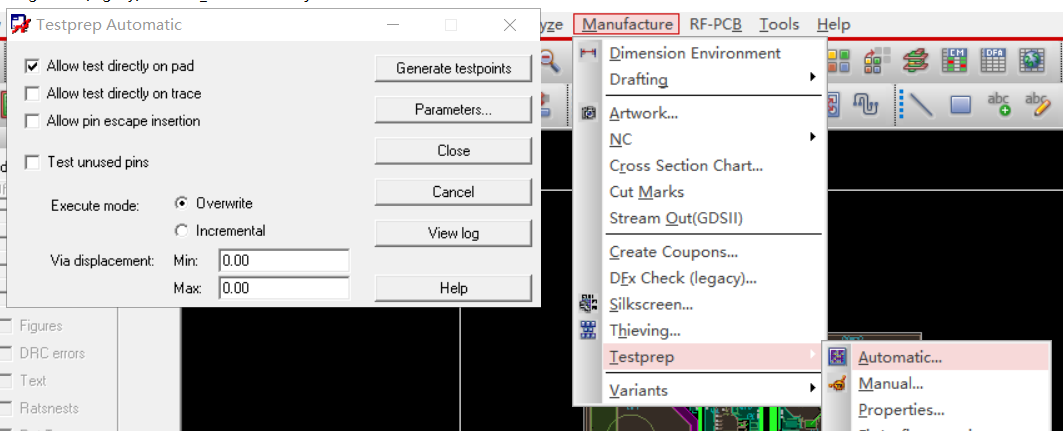

cadence allegro Allow test directly on pad:允许测试点在焊盘上,允许时将自动替换已有的过孔。Allow test directly on trace:允许测试点在信号线上,允许时测试点可以直接在信号线上。Allow pin escAPe insertion:允许从引脚上自动引出测试点。Test unused pins:无网络引脚添加测试点。

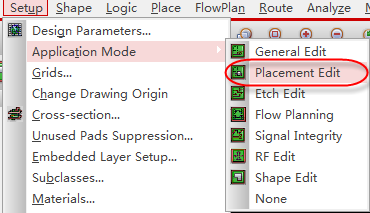

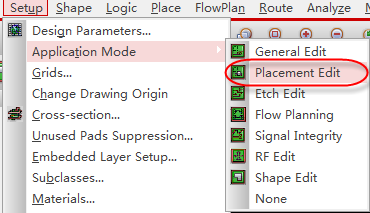

我们在使用Allegro软件进行布局布线的操作的时,会遇到很多一模一样的模块,比如电源模块、存储器模块等等。这里我们讲解一下,在PCB中怎么对一个相同的模块进行复用,具体操作如下:第一步,将已经布局布线的模块,创建一个Group,执行菜单命令Setup-APplication Mode,进行模式的选取,在下拉菜单中选择Placement Edit布局模式,如图6-1所示; 图6-1 模式选择设置示意图第二步,在Find面板中选择Symbols,其它选项都不要进行勾选,进行模型的创建,如

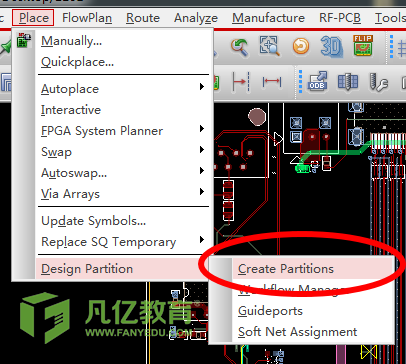

一、首先打开需要多人协助的板子,allegro点击选择Place ---Design---Create Partitions选项。二、点击进去以后,Options 栏下面 显示如下界面。三、右键点击板子空白处右键,选择加一个ShAPe 或者选择加一个矩形框。四、选择完成以后,开始框选你想要分出去的那一块。如下图,白色线框内既为要分出去的板块。

我们在使用Allegro进行PCB的绘制时,有时候需要将整个模块放置到背面去,也就是进行镜像,镜像的不仅仅是器件,还有走线、过孔等元素,这里我们就介绍一下,在Allegro软件如何将一个做好的模块,整体镜像到另一面,具体操作如下:第一步,将已经布局布线的模块,创建一个Group,执行菜单命令Setup-APplication Mode,进行模式的选取,在下拉菜单中选择Placement Edit布局模式,如图6-15所示; 图6-15 模式选择设置示意图第二步,在Find面板中选择Sy

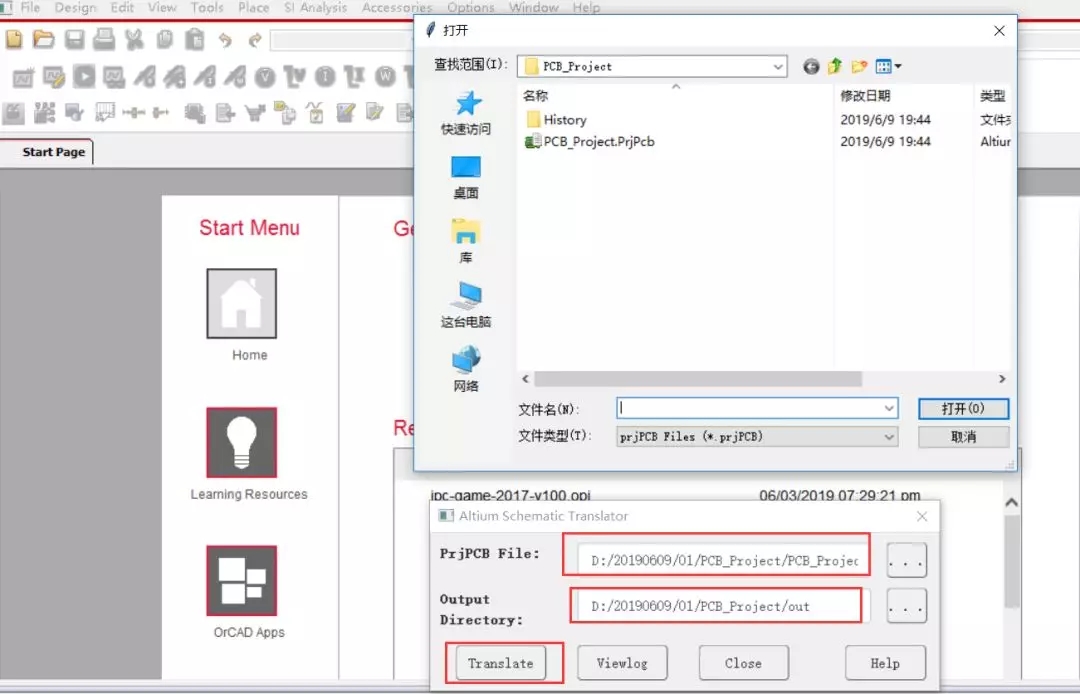

OrCAD CAPture作为行业标准的PCB原理图输入方式,是当今世界最流行的原理图输入工具之一,具有简单直观的用户设计界面。不管是用于设计模拟电路、复杂的PCB、FPGA和CPLD、PCB改版的原理图修改还是用于设计层次模块,OrCAD CAPture都能为设计师提供快速的设计输入工具。

FPGA(现场可编程门阵列)自诞生以来就一直在冲击着专用集成电路(ASIC,APplication Specific Integrated Circuit)芯片界的神经。在20世纪80年代中期,RossFreeman和他的同事从Zilog手中购买了这项技术,并着手创办了针对ASIC仿真和教育市场的Xilinx。(Zilog出自埃克森美孚石油公司,因为在20世纪70年代,人们已经开始担心石油会在30年后枯竭,这一点在今天仍然适用)。同时,Altera也以类似的技术为核心成立。 FPGA是由电路编程

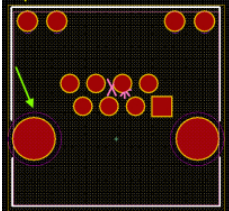

用Allegro软件里,每一个封装都有一个占地面积,一般是在Package Geometry-Place_Bound_top层画一个比器件实际尺寸大一些的ShAPe,这个ShAPe表示了单个器件在PCB上应该占用的空间大小,在做PCB设计时需要考虑不要将不同器件的占地面积堆叠重合在一起,如果放的过近,可能导致安装不方便、PCB维修有困难。

扫码关注

扫码关注