- 全部

- 默认排序

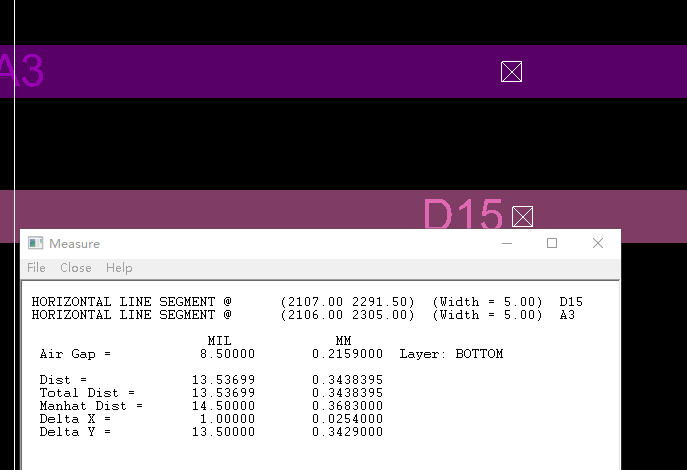

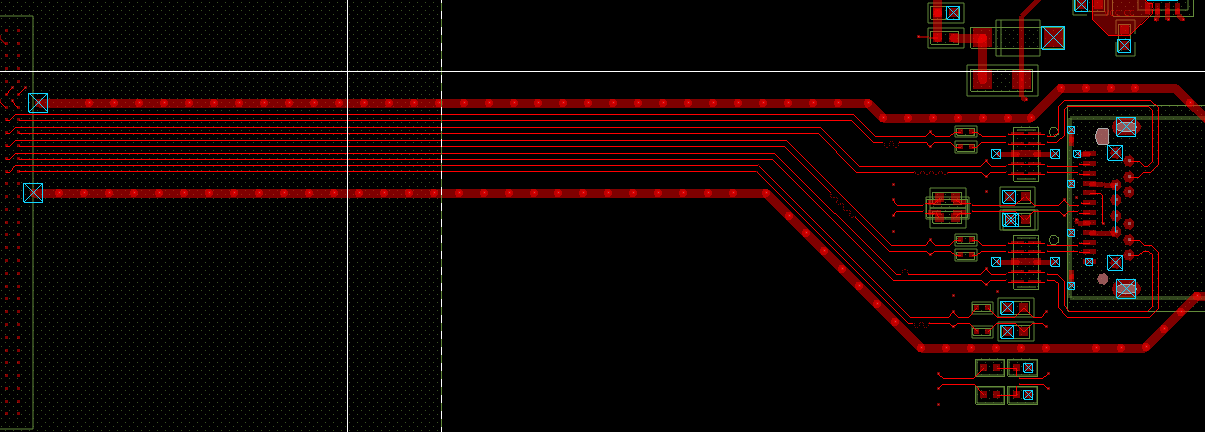

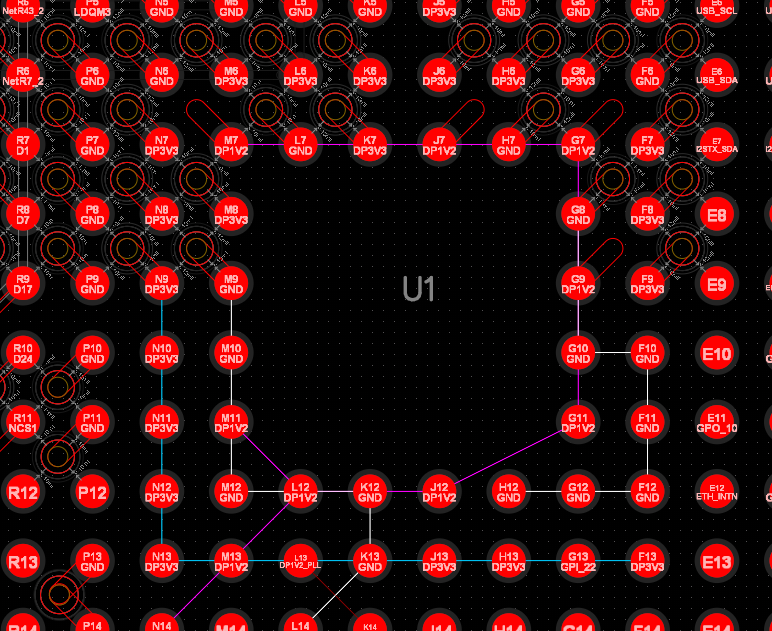

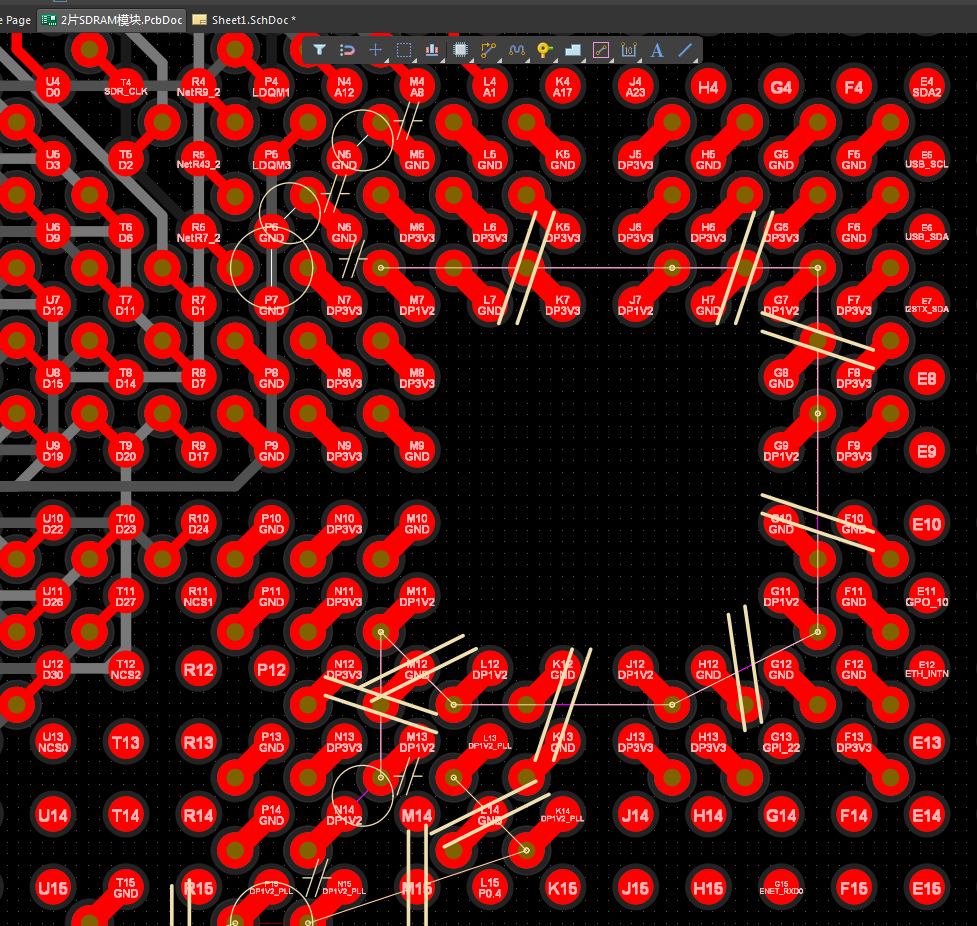

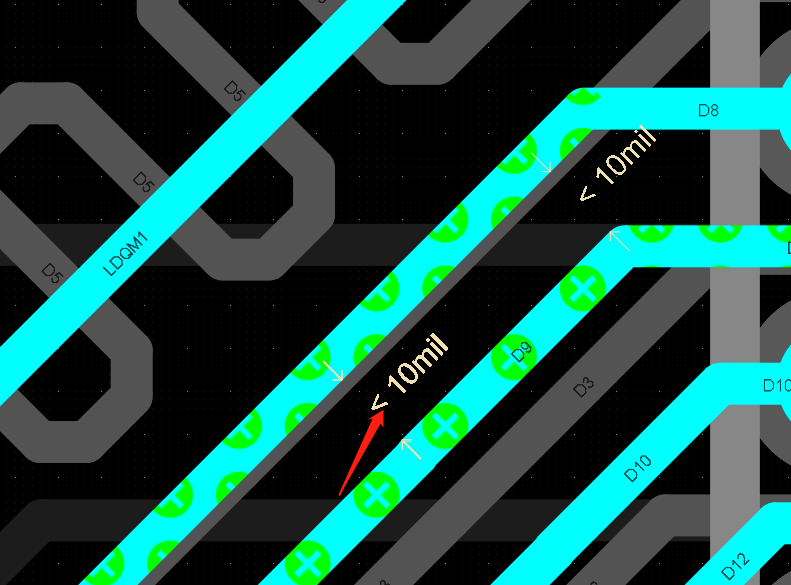

注意数据跟地址,时钟,控制之间用GND走线隔开:建议等长线的GAP也尽量满足3W,避免自身的串扰:等长不是很美观,尽量采取咬合等长,既美观也节省空间,还可以调整下美观性:上述一致原因,注意等长线的gap:其他的等长没什么问题,只要是等长美观

信号线不满足3W间距数据线和地址线之间最好画一条加粗的gnd间隔开来以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item.htm

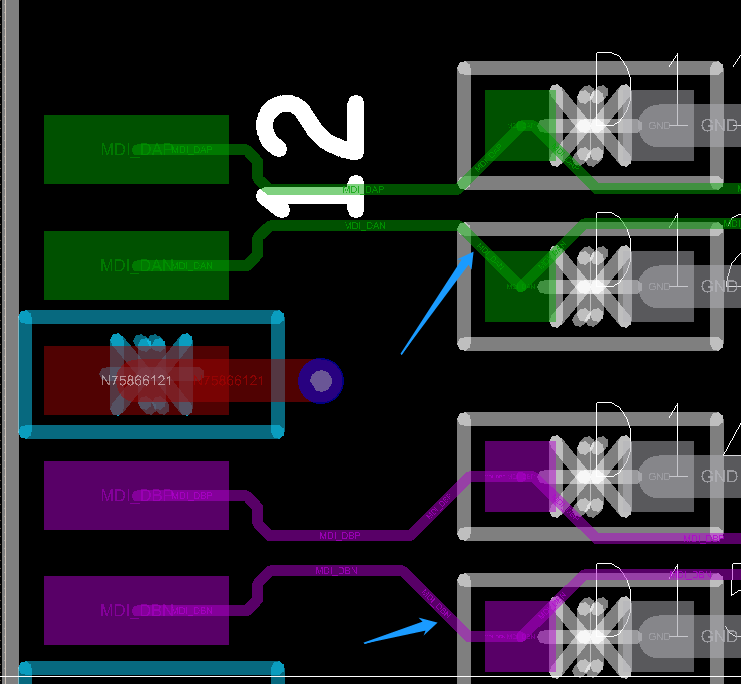

差分信号之间要用GND隔开:差分需要包地处理:此处打了两个孔,连接也两个都连接上,不然另一个孔没有意义:注意差分信号都需要包地处理:注意差分对内等长gap需要大于等于3W:没满足的都去重新等长下。差分对内等长误差为5MIL:以上评审报告来源

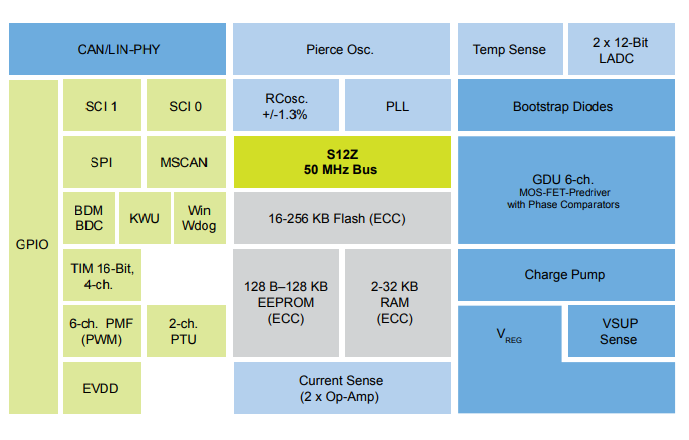

LPC55S28JBD100E ARM® Cortex®-M33微控制器 (MCU) 在安全性、性能效率和系统集成之间实现了完美平衡,适用于一般嵌入式和工业物联网市场。该MCU将Cortex-M33内核的高性能效率与多个高速接口、集成电源管

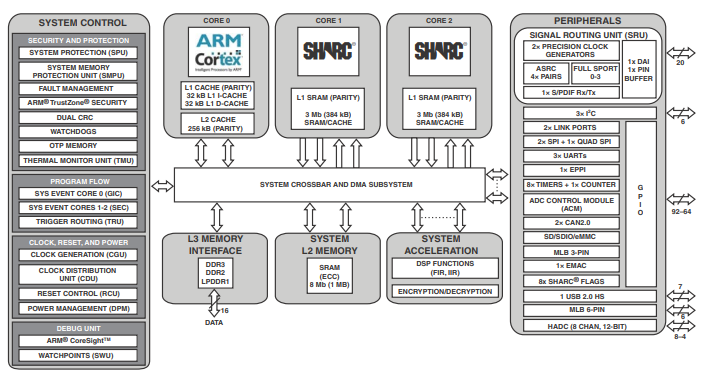

ADSP-2157x处理器属于SHARC®系列产品。ADSP-2157x SHARC处理器属于单指令多数据(SIMD) SHARC系列数字信号处理器(DSP),采用ADI公司的Super Harvard架构。这些32/40/64位浮点处理器

GND跟电源网路都没有处理:地址线都有及个别的没有跟BGA内的扇孔连接:等长线的GAP尽量大于等于3W,不要太短了:数据线一组走线尽量紧凑点:看下是否存在间距报错:等长线之间要满足3W间距原则:上述一致问题,等长线GAP满足下3W长度:间距

电源信号都没有处理:注意等长线的GAP尽量满足大于等于3W长度:可以减少串扰。注意看下xsignals分组 U16 -U17没有信号:数据跟地址用GND走线隔开:此处电源可以在电源层分割:以上评审报告来源于凡亿教育90天高速PCB特训班作业

注意数据线之间等长需要满足3W2.串组两端的信号也要加入地址信号进行等长3.地址线和数据线之间需要画一根地线进行分开4.电源需要再电源平面层进行处理,打孔进行连接以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课

差分线可以在优化一下2.晶振走内差分,且包地处理,并在地线上打过孔3.注意等长线之间需要满足3W4.网口除差分信号外,其他的都需要加粗到20mil5.存在一处开路报错以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训

注意数据线之间等长需要满足3W2.次根信号等长不满足原理图要求3..地址线之间等长也需要满足3W4.存在开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item

扫码关注

扫码关注