- 全部

- 默认排序

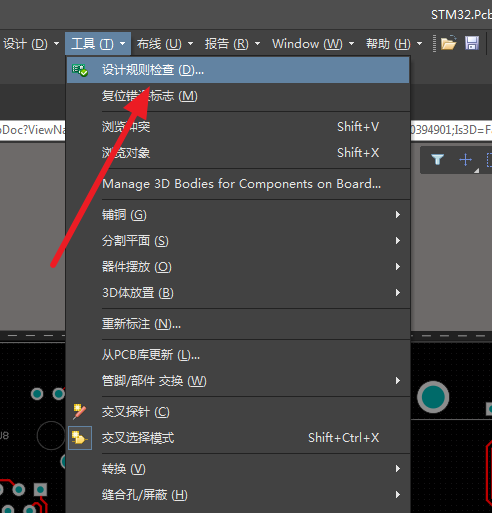

我们在进行PCB设计中,明明在规则约束器里面已经设置过相应的规则了,为什么它就是不进行报错呢?这是为什么?其实很简单,主要是两方面的操作,我们就以AD19为例进行操作吧。

在设计PCB的时候,为了满足各项设计要求的原因,我们需要设置很多的约束规则,然后设计完成之后,去进行DRC检查。DRC检查就是检查我们的PCB设计是否满足所设置的规则,常见的DRC检查有开路,短路,间距等等规则约束。接下来我们就来讲讲常见的DRC设置有哪一些。

在设计PCB的时候,为了满足各项设计要求的原因,我们需要设置很多的约束规则,然后设计完成之后,去进行DRC检查。DRC检查就是检查我们的PCB设计是否满足所设置的规则,常见的DRC检查有开路,短路,间距等等规则约束。

在DDR的设计中,需要对数据线及地址线进行分组及等长来满足时序匹配,通常DDR的数据线之间的长度误差需要保证在50mil以内,地址线的长度误差需要保证在100mil以内。执行菜单命令【设计】-【规则】或者使用快捷键DR打开规则约束器,在“H

AD软件中怎么添加不同元素之间的间距规则呢答:AD软件提供了某一个元素针对其他元素之间的间距规则的设置。首先执行菜单命令【设计】-【规则】或者快捷键DR打开规则约束编辑器,然后在间距规则Clearance里面添加一个新的规则,如图1所示图1

扫码关注

扫码关注