- 全部

- 默认排序

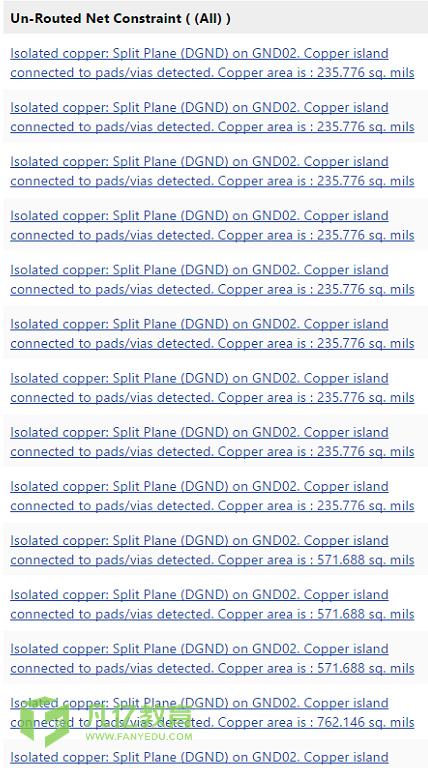

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。比如今天要讲解的DRC报错中的“Isolated copper:Split pllane....”的报错,为了方便大家了解这项报错,我们找到了素材图片如下:

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。

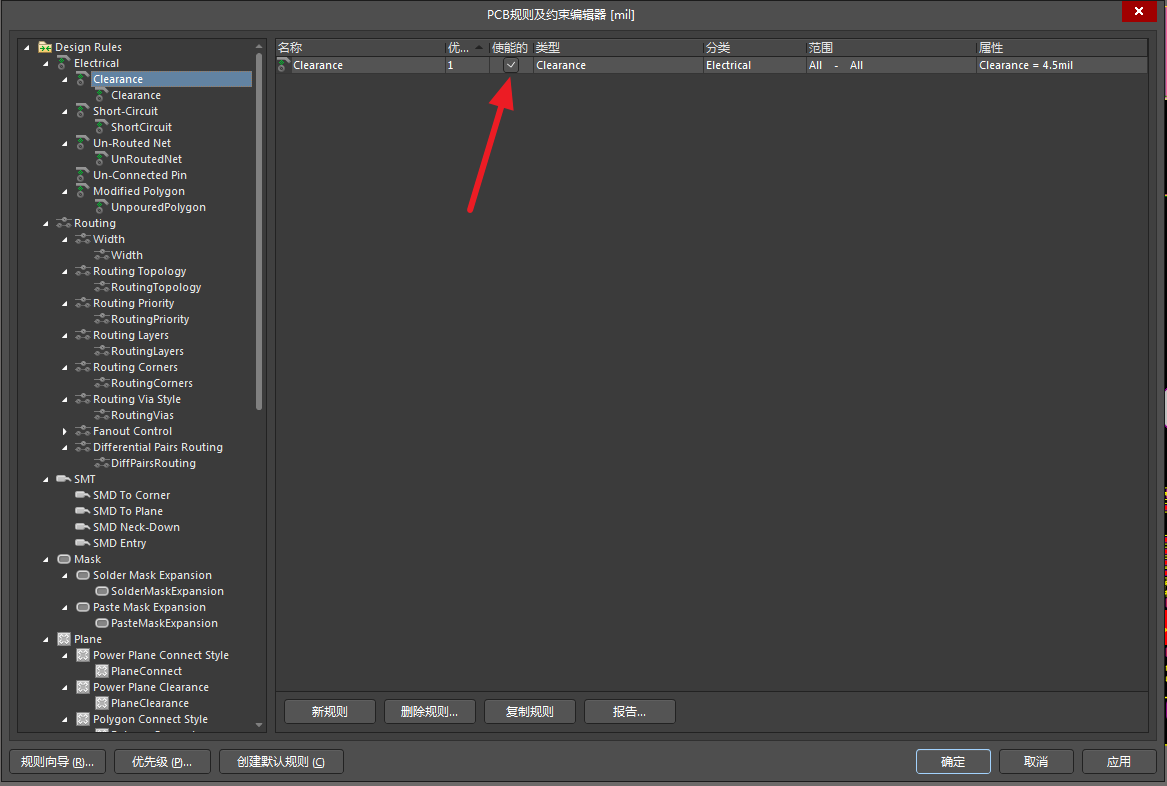

我们在根据PCB板的要求,在规则编辑器里面加入了很多对应的规则。有比如:间距规则,线宽规则,短路等都是非常重要的电气规则规则,及其关乎到我们最后打样的关键。可是很多时候我们明明是在规则编辑器里面设置了规则的,为什么在我们规则之外的时候它竟然不报错呢?是哪里设置不对吗?

规则报错some rules have incorroect definitions,would you like to correct them?这是啥原因哪里不正确

扫码关注

扫码关注