- 全部

- 默认排序

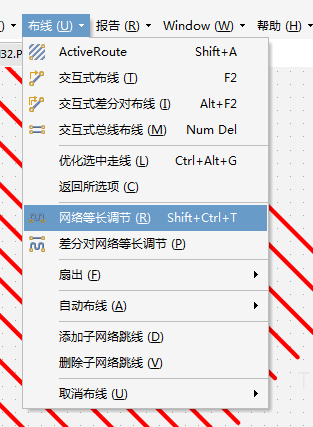

本视频采用我们的Altium designer 19软件进行我们的差分走线的等长的处理,同时简单介绍我们的差分走线和等长走线时候的注意事项,以及我们的等长目标线的确定和我们的等长的一些快捷键的小技巧。

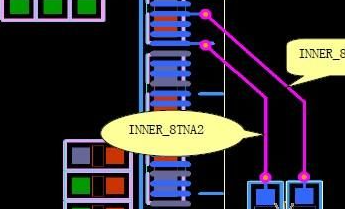

★ 掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★交互式模块化快速布局★BGA扇孔出线的方式、BGA的快速拉线方法★菊花链拓扑结构的认识及设置★掌握蛇形等长走线,掌握★了解常见EMC的PCB处理方法3W规则的应用

★掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★交互式模块化快速布局★BGA扇孔出线的方式、BGA的快速拉线方法★掌握DDR的设计方法★掌握蛇形等长走线,掌握3W规则的应用★了解常见EMC的PCB处理方法。

★掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程★掌握DDR3设计的知识要点★掌握3W原则的PCB设计★了解T点拓扑结构及设计规则★掌握蛇形等长走线,阻碍线的使用★掌握叠层阻抗计算的方法★了解常见EMC的PCB处理方法

1. 掌握PCB设计常用的设计技巧及熟悉PCB设计的整体流程 2. 掌握DDR3设计的知识要点 3.掌握3W原则的PCB设计 . 了解菊花链拓扑结构及设计规则 . 掌握蛇形等长走线

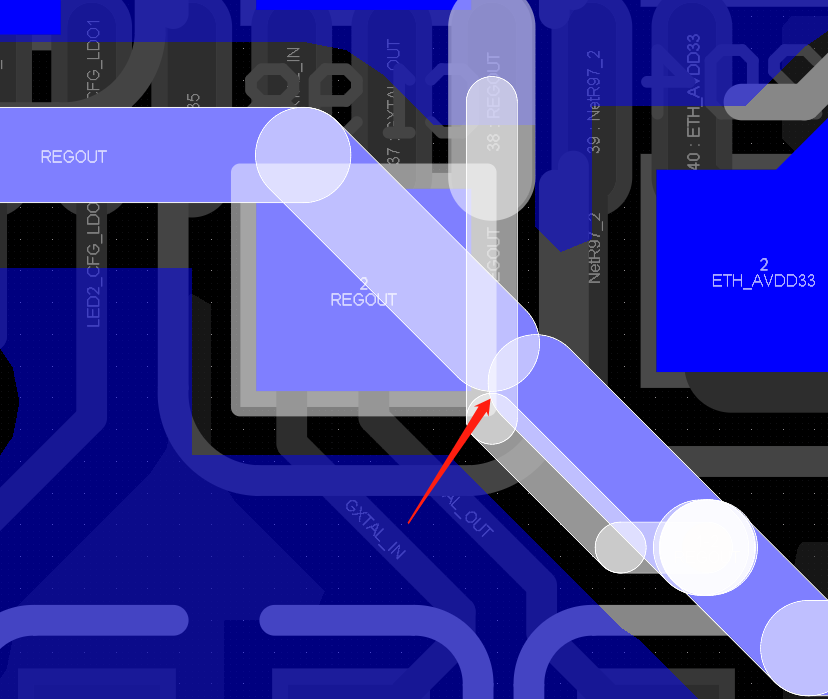

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

Altium Designer 21在之前版本的基础上对蛇形等长功能进行了优化,大大提高了设计的效率和规范性,具体改进可以参考以下说明。1.1新增两种等长样式 在之前的版本设计当中,等长设计时只有单一的U形等长。Altium Designe

走线未完全连接上TX等长误差100mil,时钟信号也要进行等长走线不要有直角其他没什么问题以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.c

扫码关注

扫码关注