- 全部

- 默认排序

大家好,我是龙学飞,欢迎大家学习我的本套课程,这套课程主要给大家介绍基于Realtek RTL8306平台路由器产品4层PCB设计的全过程,包括PCB设计预处理---PCB设计分析---PCB原理图、结构导入---PCB布局处理---PCB设计规则添加---PCB设计布线处理---PCB设计等长处理---电源平面分割处理---丝印调整---DRC检查---GERBER输出---文件归档等PCB设计的整个流程,通过学习本视频,可以迅速地掌握4层初等难度PCB设计方法及思路。

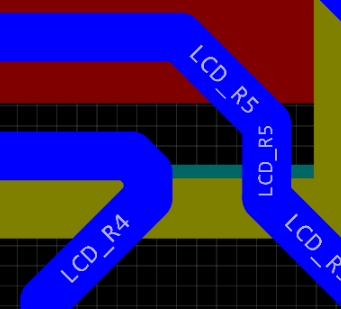

本视频采用我们的Altium designer 19软件进行我们的差分走线的等长的处理,同时简单介绍我们的差分走线和等长走线时候的注意事项,以及我们的等长目标线的确定和我们的等长的一些快捷键的小技巧。

PCB设计信号等长分析

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是我们俗称的PCB信号等长处理。

SDRAM信号线等长处理

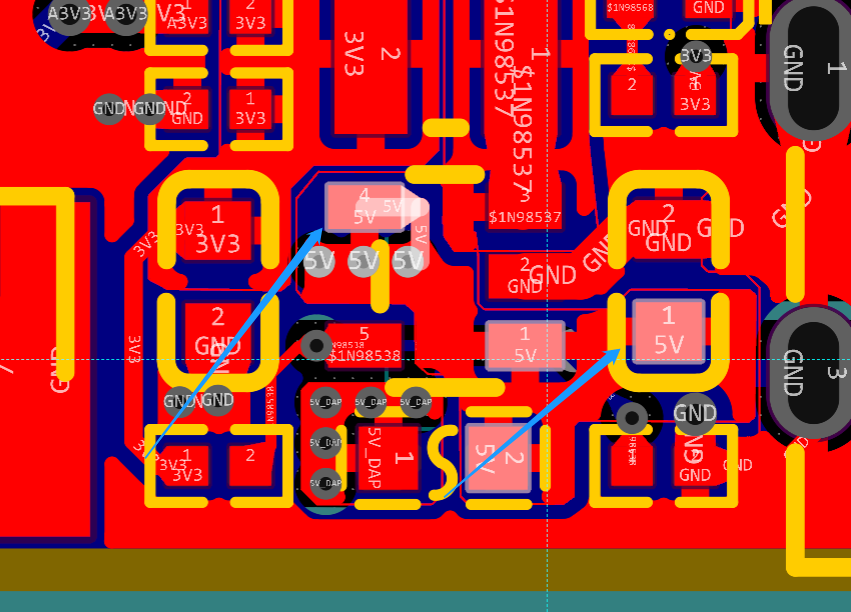

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

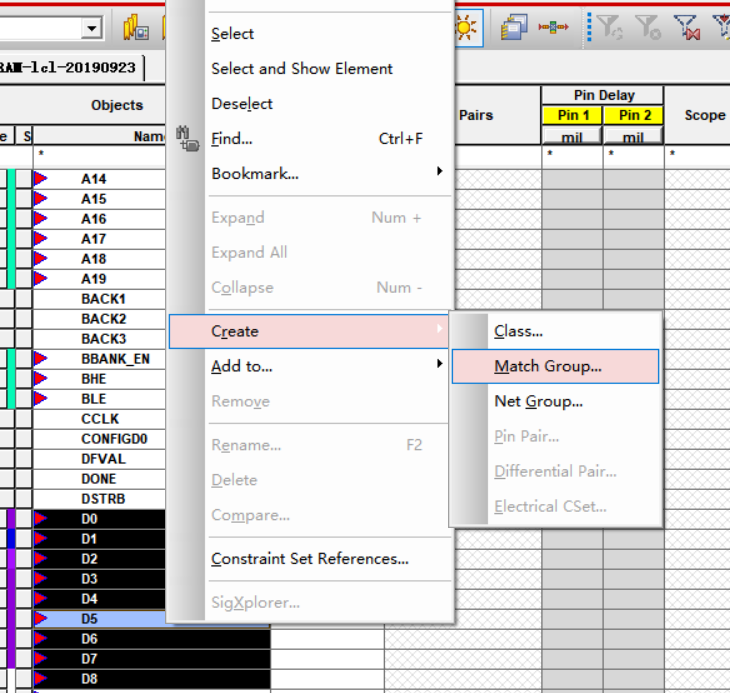

答:我们对于高速信号传输,比如差分信号、一组总线传输,都需要对其进行时序等长处理,在16.6版本以上,Allegro软件推出了自动等长的功能,在空间足够的情况下,是可以采用自动等长的功能,省去手动绕等长的时间,具体操作步骤如下所示:

答:PCB设计中有一些信号组需要进行等长处理,以保证组内信号时序要求。第一步,点击Setup-Constraints-Constraint Manager选项,调出规则管理器,如图6-269所示;

PADS蛇形等长处理

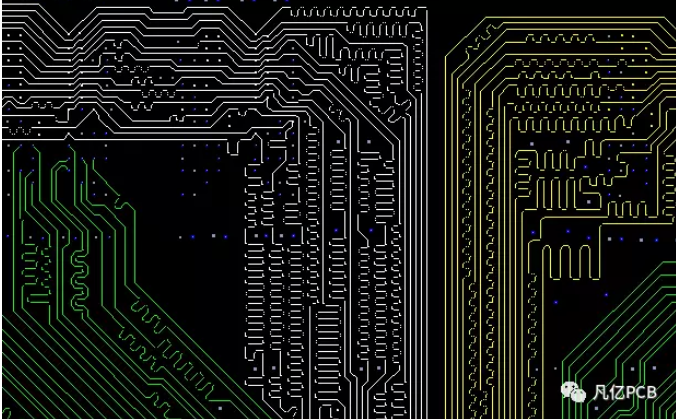

在做PCB设计时,为了满足某一组所有信号线的总长度满足在一个公差范围内,通常要使用蛇形走线将总长度较短的信号线绕到与组内最长的信号线长度公差范围内,这个用蛇形走线绕长信号线的处理过程,就是俗称的PCB信号等长处理。如图6-59示。图6-59

1.电源输入的滤波电容应该靠近输入管脚放置2.【问题分析】:注意等长线之间需要满足3W规则3.【问题分析】:USB需要进行等内等长处理,等长误差为5mil4.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-

差分线这里需要调整走线尽量不要有直角锐角这里是输出走线应该加粗处理最好铺铜处理。SD卡所有信号线要做等长处理,以时钟线为目标,目标控制在300mil以内。这个差分在这里另一根就断了,不耦合对内也不等长。很多的线间距都不满足3w原则自己调整一

电源模块反馈电路错误,r15接入反馈电源到r14在到5号管脚。2.晶振布局布线错误3.typec差分对内误差控制5mil以内,尽量避免出现不耦合4.TF卡所有信号线要整组 ,做等长处理以时钟线为目标,目标控制在300mil以内。

扫码关注

扫码关注