- 全部

- 默认排序

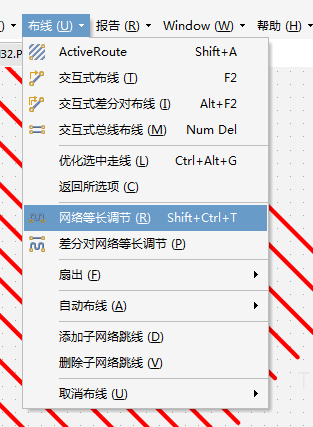

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

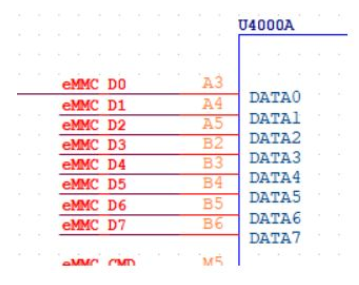

DDR电路简介RK3588 DDR 控制器接口支持 JEDEC SDRAM 标准接口,原理电路16位数据信号如图8-1所示,地址、控制信号如图8-2所示,电源信号如图8-3所示。电路控制器有如下特点:1、兼容 LPDDR4/LPDDR4X/

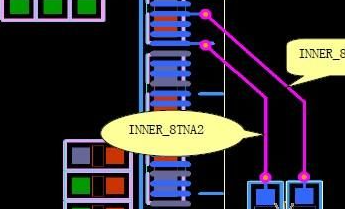

EMMC电路简介EMMC (Embedded Multi Media Card)是MMC协会订立、主要针对手机或平板电脑等产品的内嵌式存储器标准规格。EMMC在封装中集成了一个控制器,提供标准接口并管理闪存。原理电路8位数据信号如图8-38

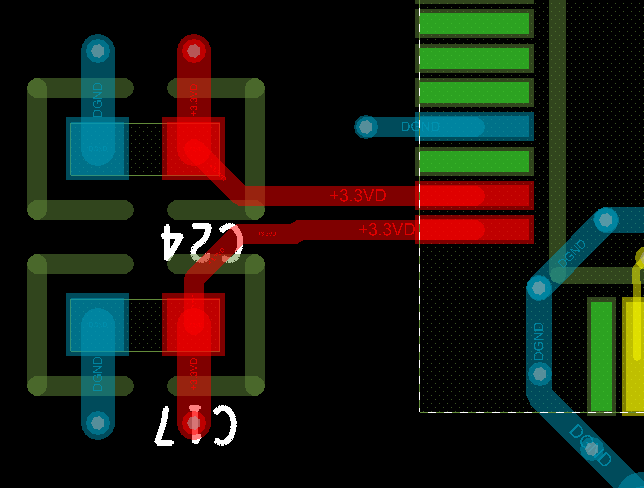

1.布局应按照先大后小原则布局,大器件打孔连接到小器件再连接到芯片管脚2.有一个数据信号等长不到位3.要保持先后线宽一一致,走线出芯片焊盘后尽快加粗以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接

PoE供电器(Power over Ethernet Injector)是一种用于给网络设备提供电力的设备。它可以通过网络线缆将电力和数据信号传输到远程设备,从而方便了设备的安装和布线。01PoE供电器组成PoE供电器一般由以下几个组成部分

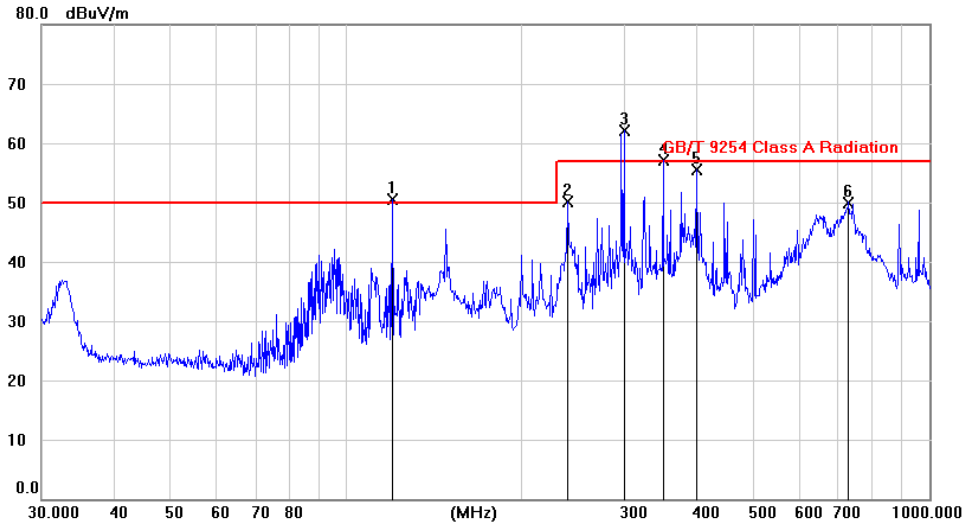

最近想起来,以前在做EMI整改的时候,出现过低频辐射超标,类似下面这种。一般这种问题,我们都会说是时钟线引起的问题。我之前做的产品是摄像头,时钟线加十几根数据线。有一次处理完时钟线后还是超标,因为正好数据线上都串有电阻,我就将电阻都改成了磁珠,想消除因为数据线引起的辐射,改完之后发现还是超标,看不到

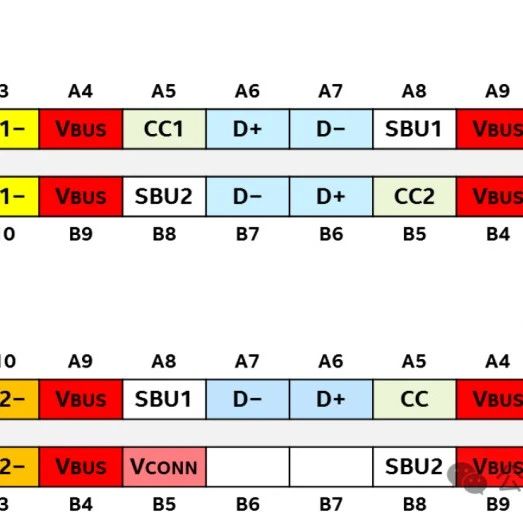

Type-C接口图VBUS 和GND:电源和地线引脚。其中VBUS是供电端(Source)向用电端(Sink)供电的电压线。D 和D-:用于传输USB 2.0差分数据信号,插座中有两对D 、D-引脚是防止插头反插或线缆方向反插的冗余设计,实际只有一对差分数据信号可供使用。TX 、TX-和 RX 、R

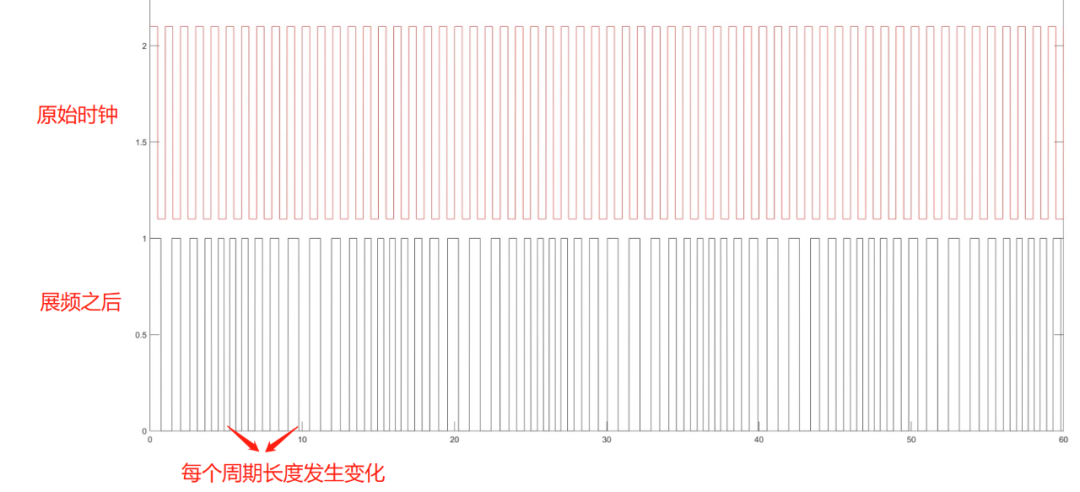

先前我们说了说:为什么时钟信号比数据信号更容易引起辐射超标?为什么时钟信号比数据信号更容易引起辐射超标?并且做了试验,如果认真看过的话,就会明白,周期性的信号是窄带频谱,特定的频率的幅值会很高,这对认证测试来说非常的不利。而一般时钟信号都是周期信号,这在电路中是少不了的。有没有什么办法,改造下时钟的

扫码关注

扫码关注