- 全部

- 默认排序

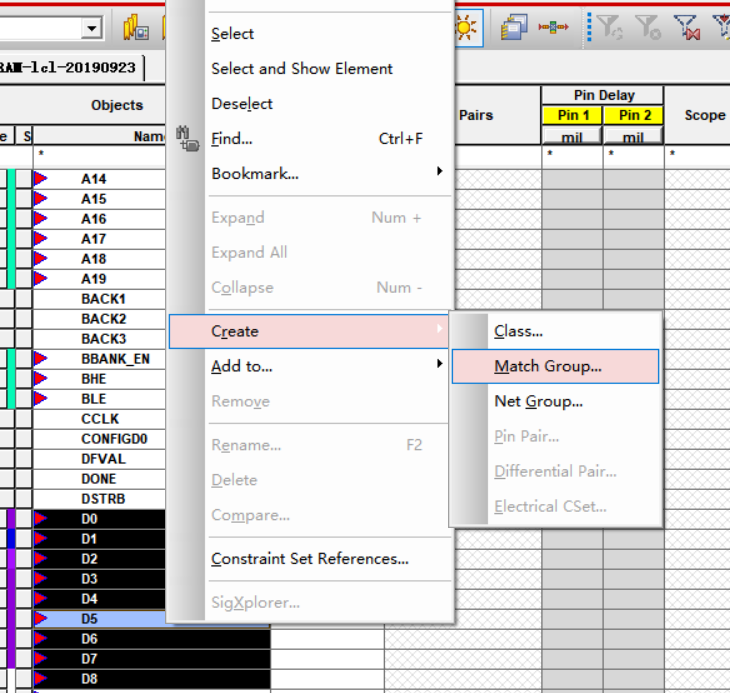

一、8 层 Allegro T 点星型拓核心板课程详情这个是一个非常经典的 T 点星型拓核心板设计,主要采用飞思卡尔 IMX6 主控芯片,4 片DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等。

此Altium Designer视频是专门针对 DDR3 设计来的,采用飞思卡尔 IMX6 主控芯片, 4 片 DDR3 同层设计,采用 DDR3 常见的 T 点拓扑结构,一个大 T 点两个小 T 点的方式。讲解了 DDR3 设计的信号 class 分组,信号的同组同层及常用规则注意事项,信号完整性的规划等,让学习者知其然知其所以然。

一、PADS8层DDR3 Fly-by拓扑结构视频课程详情本pads视频课程基于飞思卡尔 i.MX6 处理器的 8层PCB设计,重点介绍 DDR3 内存的设计思路,一共四颗 DDR3,采用菊花链(Fly-By)的拓扑结构。讲解了 DDR3 设计的信号 class分组,信号的同组同层布线、信号时序等长及常用规则注意事项、信号完整性、电源完整性的规划等。

SDRAM信号线等长处理

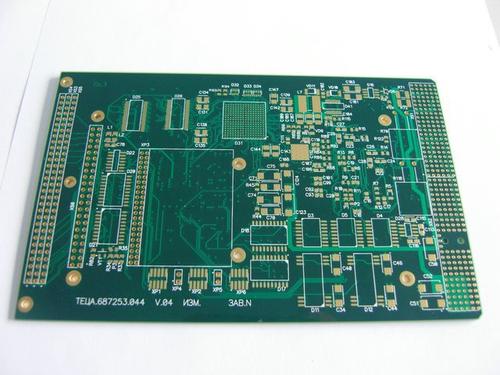

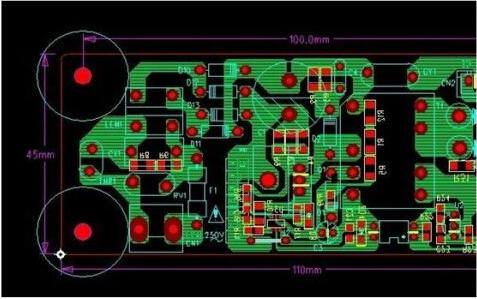

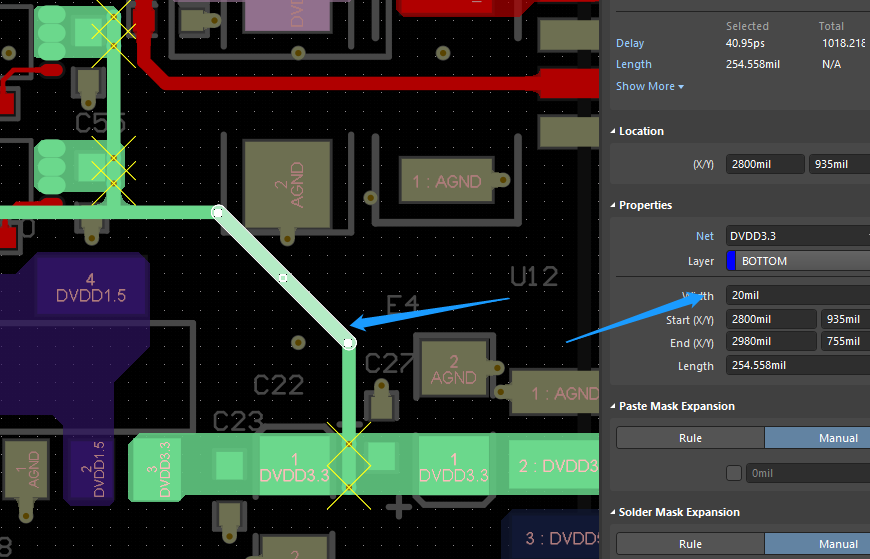

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

确认一下此处输出是否满足载流,后期自己加宽走线2.电容尽量靠近管脚摆放,尽量均匀摆放3.走线可以在优化一下,尽量不要有锐角4.存储器要分组走线,同组同层,需要等长处理,误差100mil5.走线注意拓扑结构,这个应该是采取菊花链的走线方式,后

扫码关注

扫码关注