- 全部

- 默认排序

什么是集成电路设计

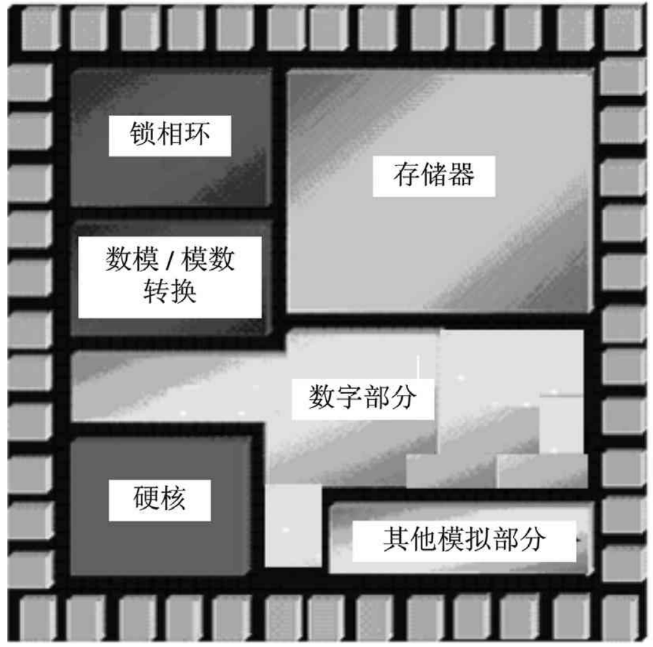

集成电路设计,根据当前集成电路的集成规模,亦可称之为超大规模集成电路设计,是指以集成电路、超大规模集成电路为目标的设计流程。集成电路设计通常是以“模块”作为设计的单位的。例如,对于多位全加器来说,其次级模块是一位的加法器,而加法器又是由下一级的与门、非门模块构成,与、非门最终可以分解为更低抽象级的CMOS器件。下面就让我们进一步的了解集成电路设计的相关知识。 集成电路设计介绍 集成电路设计的流程一般先要进行软硬件划分,将设计基本分为两部分:芯片硬件设计和软件协同设计。芯片硬件设计包括: 1

对于电子工程师来说,使用最广泛的中规模组合逻辑集成电路,莫过于二进制并行加法器、译码器、编码器、多路选择器和多路分配器等,其中二进制并行加法器是最常用的集成电路逻辑部件,今天我们来谈谈二进制并行加法器。二进制并行加法器一种能产生两个二进制数

IC系统是什么?对于这个问题,不同的工程师大概会给出不同的答案。算法工程师会说IC系统是完成特定功能的硬件;架构设计工程师会说IC包括控制、运算、存储部分;电路设计工程师会说是加法器、乘法器、与非门、运算放大器、开关电容等的搭配。但事实上这

扫码关注

扫码关注