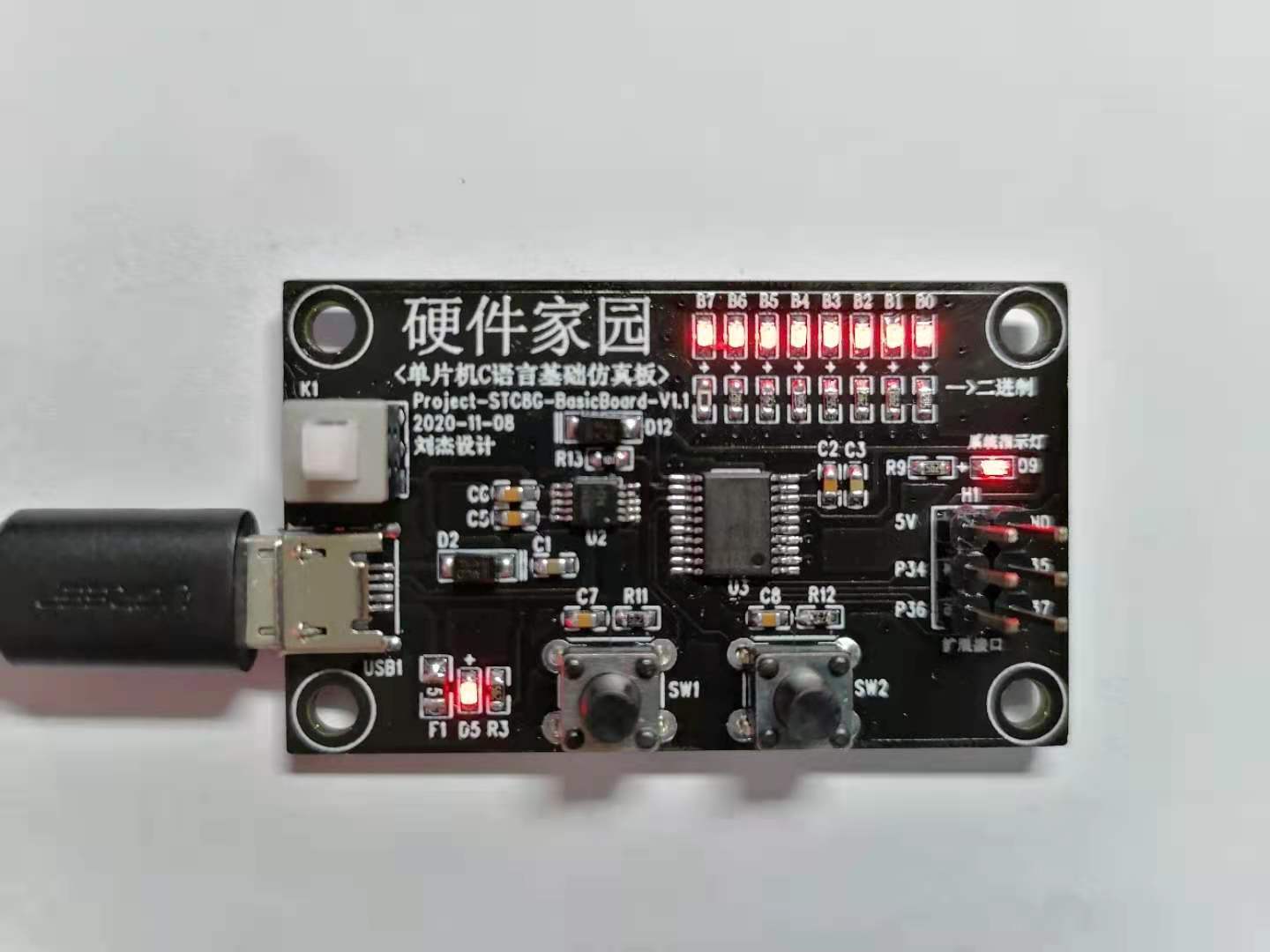

对于电子工程师来说,使用最广泛的中规模组合逻辑集成电路,莫过于二进制并行加法器、译码器、编码器、多路选择器和多路分配器等,其中二进制并行加法器是最常用的集成电路逻辑部件,今天我们来谈谈二进制并行加法器。

二进制并行加法器一种能产生两个二进制数算术和的组合逻辑部件,按照其进位方式的不同,可分为串行进位二进制并行加法器和超前进位二进制并行加法器两种类型。

1、串行进位二进制并行加法器

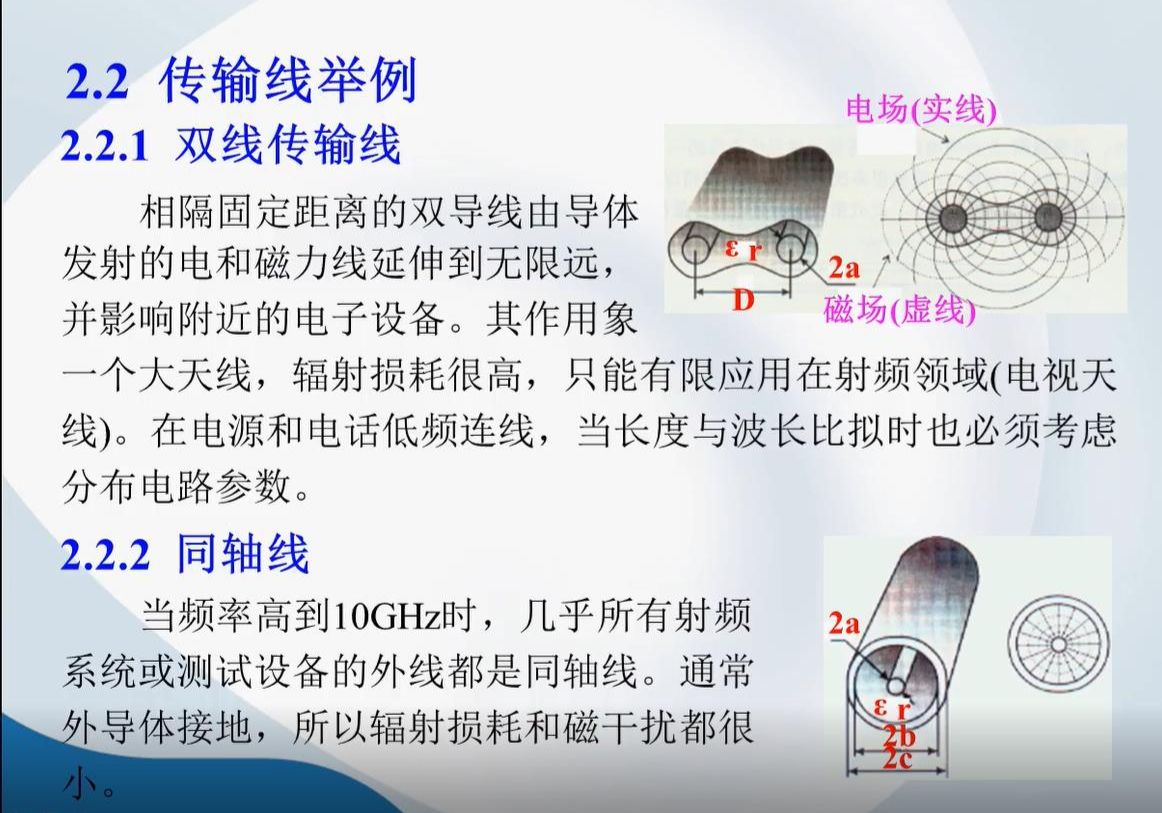

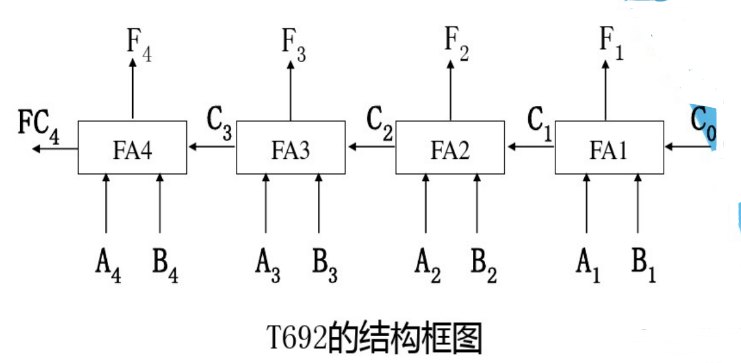

串行进位二进制并行加法器是由全加器级联组成,高位的进位输出依赖于低位的进位输入,典型产品有四位二进制并行加法器T692,如图所示。

被加数和家属的各位能同时并行到达各位的输入端,而各位全加器的进位输入则是按照由低位向高位逐级串行传递的,各进位形成一个进位链。由于每一位相加的和都与本位进位输入有关,所以,最高位必须等到各低位全部相加完成并送来进位信号之后才能产生运算结果,但缺点是运算速度较慢,而且位数越多,速度越低,所以为解决该缺陷,超前进位二进制并行加法器诞生了。

2、超前进位二进制并行加法器

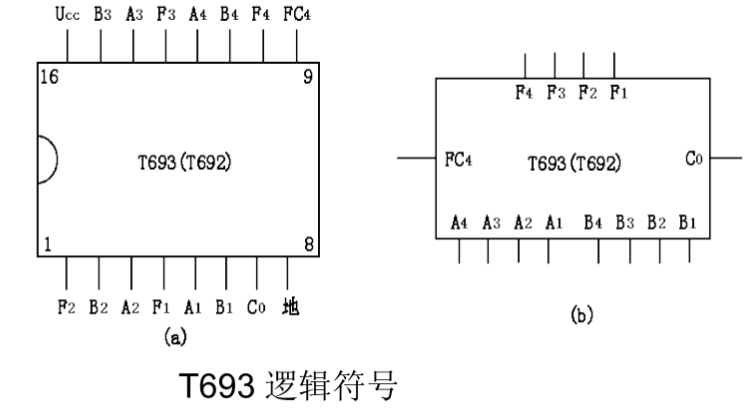

超前进位(又称先行进位)二进制并行加法器,是根据输入信号同时形成各位向高位的进位,然后同时产生各位的和。典型产品有四位二进制并行加法器T693,如图所示。

扫码关注

扫码关注