一、静电放电波形和能量频谱

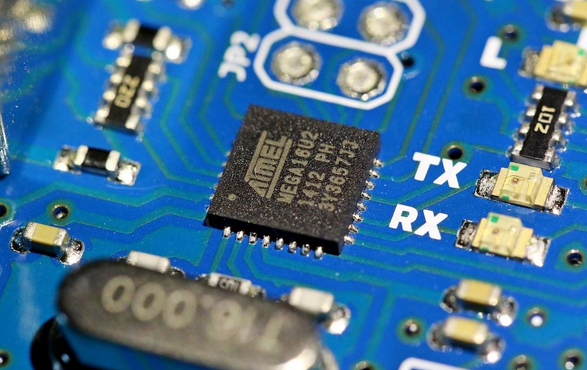

静电放电(ESD)理论研究的已经相当成熟,为了模拟分析静电事件,前辈电路设计了很多静电放电模型。

常见的静电模型有:人体模型(HBM),带电器件模型,场感应模型,场增强模型,机器模型和电容耦合模型等。芯片级一般用HBM做测试,而电子产品则用IEC 6 1000-4-2的放电模型做测试。为对 ESD 的测试进行统一规

范,在工业标准方面,欧共体的 IEC 61000-4-2 已建立起严格的瞬变冲击抑制标准;电子产品必须符合这一标准之后方能销往欧共体的各个成员国。因此,大多数生产厂家都把 IEC 61000-4-2看作是 ESD 测试的事实标准。我国的国家标准(GB/T 17626.2-1998)等同于I EC 61000-4-2。大多是实验室用的静电发生器就是按 IEC 6 1000-4-2的标准,分为接触放电和空气放电。静电发生器的模型。 放电头按接触放电和空气放电分尖头和圆头两种。

IEC 61000-4-2的静电放电的波形如,可以看到静电放电主要电流是一个上升沿在1nS左右的一个上升沿,要消除这个上升沿要求ESD保护器件响应时间要小于这个时间。静电放电的能量主要集中在几十MHz到500MHz,很多时候我们能从频谱上考虑,如滤波器滤除相应频带的能量来实现静电防护。其放电频谱如下,这个图是我自己画的,只能定性的看,不能定量。

IEC 61000-4-2规定了几个试验等级,目前手机CTA测试执行得是3级,即接触放电6KV,空气放电8KV。很多手机厂家内部执行更高的静电防护等级。

当集成电路( IC )经受静电放电( ESD)时,放电回路的电阻通常都很小,无法限制放电电流。例如将带静电的电缆插到电路接口上时,放电回路的电阻几乎为零,造成高达数十安培的瞬间放电尖峰电流,流入相应的 IC 管脚。瞬间大电流会严重损伤 IC ,局部发热的热量甚至会融化硅片管芯。 ESD 对 IC的损伤还包括内部金属连接被烧断,钝化层受到破坏,晶体管单元被烧坏。

ESD 还会引起 IC 的死锁( LATCHUP)。这种效应和 CMOS 器件内部的类似可控硅的结构单元被激活有关。高电压可激活这些结构,形成大电流信道,一般是从 VCC 到地。串行接口器件的死锁电流可高达 1A 。死锁电流会一直保持,直到器件被断电。不过到那时, IC 通常早已因过热而烧毁了

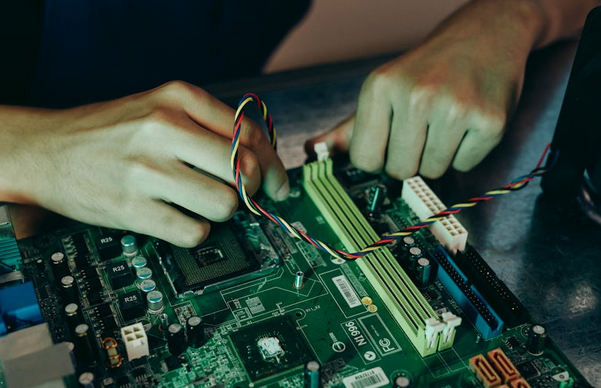

电路级ESD防护方法

1、并联放电器件。

常用的放电器件有TVS,齐纳二极管,压敏电阻,气体放电管等。

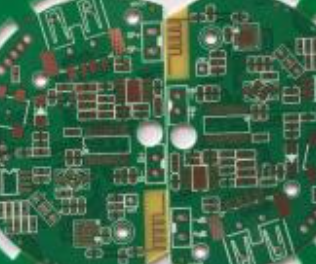

1.1、齐纳二极管( Zener Diodes ,也称稳压二极管 ) 。 利用齐纳二极管的反向击穿特性可以保护 ESD敏感器件。但是齐纳二极管通常有几十 pF 的电容,这对于高速信号电路设计(例如 500MHz)而言,会引起信号畸变。齐纳二极管对电源上的浪涌也有很好的吸收作用。

1.2、瞬变电压消除器 TVS(Transient Voltage Suppressor) 。 TVS 是一种固态二极管,专门用于防止 ESD 瞬态电压破坏敏感的半导体器件。与传统的齐纳二极管相比, TVS 二极管 P/N 结面积更大,这一结构上的改进使 TVS 具有更强的高压承受能力,同时也降低了电压截止率,因而对于保护手持设备低工作电压回路的安全具有更好效果。

TVS二极管的瞬态功率和瞬态电流性能与结的面积成正比。该二极管的结具有较大的截面积,可以处理闪电和 ESD所引起的高瞬态电流。TVS也会有结电容,通常0.3个pF到几十个pF。TVS有单极性的和双极性的,使用时要注意。手机上用的TVS大约0.01$,低容值的约2-3分$。

1.3、多层金属氧化物结构器件 (MLV),大陆一般称为压敏电阻。 MLV也可以进行有效的瞬时高压冲击抑制,此类器件具有非线性电压 - 电流 ( 阻抗表现 ) 关系,截止电压可达最初中止电压的 2 ~ 3倍。这种特性适合用于对电压不太敏感的线路和器件的静电或浪涌保护,如电源回路,按键输入端等。手机用压敏电阻约0.0015$,大约是TVS价格的1/6,但是防护效果没有TVS好,且压敏电阻有寿命老化。

2、串联阻抗

一般可以通过串联电阻或者磁珠来限制ESD放电电流,达到防静电的目的。如手机的高输入阻抗的端口可以串1K欧电阻来防护,如ADC,输入的GPIO,按键等。不要担心0402的电阻会被打坏,实践证明是打不坏的。这里不详细分析。用电阻做ESD防护几乎不增加成本。如果用磁珠,磁珠的价格大 约0.002$,和压敏电阻差不多.

3、增加滤波网络

前面提到了静电的能量频谱,如果用滤波器滤掉主要的能量也能达到静电防护的目的。

对于低频信号,如GPIO输入,ADC,音频输入可以用1k+1000PF的电容来做静电防护,成本可以忽略,性能不比压敏电阻差,如果用1K+50PF的压敏电阻(下面讲的复合防护措施),效果更好,经验证明这样防护效果有时超过TVS。

对于射频天线的微波信号,如果用TVS管,压敏等容性器件来做静电防护,射频信号会被衰减,因此要求TVS的电容很低,这样增加ESD措施的成本。对于微波信号可以对地并联一个几十nH的电感来为静电提供一个放电通道,对微波信号几乎没有影响,对于900MHZ和1800MHz的手机经常用22nH的电感。这样能把静电主要能量频谱上的能量吸收掉很多。

4、复合防护

有一种器件叫EMI filter,他有很好的ESD防护效果,EMI filter也有基于TVS管的和基于压敏电阻的,前者效果好,但很贵,后者廉价,一般4路基于压敏电阻的EMI价格在0.02$.

实际应用中可以用下面的一个电阻+一个压敏电阻的方式。他既有低通滤波器的功能,又有压敏电阻的功能,还有电阻串联限流的功能。是性价比最好的防护方式,对于高阻信号可以采用1K电阻+50PF压敏;对于耳机等音频输出信号可以采用100欧电阻+压敏电阻;对于TP信号串联电阻不能太大否则影响TP的线性,可以采用10欧电阻。虽然电阻小了,低通滤波器效果已经没有了,但限流作用还是很重要的。

5、增加吸收回路

可以在敏感信号附件增加地的漏铜,来吸收静电。道理和避雷针原理一样。

在信号线上放置尖端放电点(火花隙)在山寨手机设计中也经常应用。

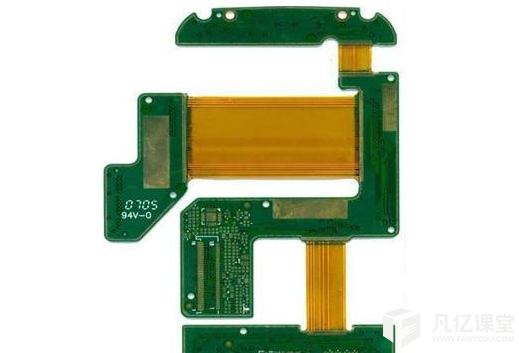

翻盖机受话器上TVS管或压敏电阻应该放在哪?

很多人理解静电防护器件在layout时要靠近端口摆放,翻盖机或者滑盖机受话器(receiver,rec)上的TVS或压敏电阻要放在上板靠近rec的地方。其实不然,请看下面分析。

这是一个翻盖机或者滑盖机,的等效电路,TVS在上板,主IC在主板,中间用比较长的FPC连接。rec是个线圈,不怕静电,怕静电的是IC。

中间的电感分别是FPC上地网络和信号线的等效电感。当静电打在rec上时,由于TVS的钳位作用和等效电容存在,静电放电瞬时REC信号线上的电压Ub和小板的电压Ug可以看成相等的,静电荷要从FPC的地网络转移一部分到主板的地上,这时会在主板的地和小板的地之间产生一个压差Ug-0=Ug。对于信号线如果是高祖状态,即使FPC存在更大的等效电感,但是因为高阻抗不会产生电流,Ua和Ub可以看成是一致的,这样Ua=Ub=Ug,也就是芯片端和地之间会产生一个电压差,这个压差几乎等于放电瞬间小板地合主板地的电压差,这个电压差如果很大会使IC损坏。电压差大小取决于ESD放电的等级和FPC地上的等效阻抗和电感。如果是非高祖信号会有一点电流,电流大了芯片也就坏了。这样也可以近似看成Ua=Ub=Ug。因此TVS或压敏电阻放在上板如果静电达到rec上会有问题。

假如静电打在小板的地上,由于TVS或压敏的钳位和等效电容,同样Ub=Ug。由于FPC的地上等效电感存在,Ug和主板地会存在压差。信号线上没有电流Ua=Ub=Ug。Ua加在芯片端口上会打坏芯片。

假如静电打在主板地上,主板地上电荷部分会往小板地转移,产生电流,电流在FPC地等效电感上产生电压,同样会在主板地和小板地之间的电压会直接加在芯片两端烧坏芯片。

如果TVS或压敏电阻加在主板上,由于TVS或压敏的钳位作用,Ua和地之间电压不会太高起到保护芯片的作用。静电放在rec上,电流传导到主板上被TVS吸收掉,电荷打在小板地和主板地上都和信号线没有关系。

静电防户器件应该放在哪?

rec情况如此,其他信号线电源也如此。

上面分析的是用FPC连接两个板的情况,其实即使一块板子地上也会有阻抗的存在,这么看静电防护器件靠近芯片越近越好,即保护谁就靠近谁。特别是没有完整地层的板子。

但有个问题如果靠近芯片在端口到TVS这段走线会存在大的放电电流和电压,这样会干扰到与其相邻的为保护的信号线。鉴于手机主板有完整地层,地上等效阻抗比较小,建议把静电防护器件放在主板的接口处,但不能放在小板,按键板等上面。

扫码关注

扫码关注