啥是反射?

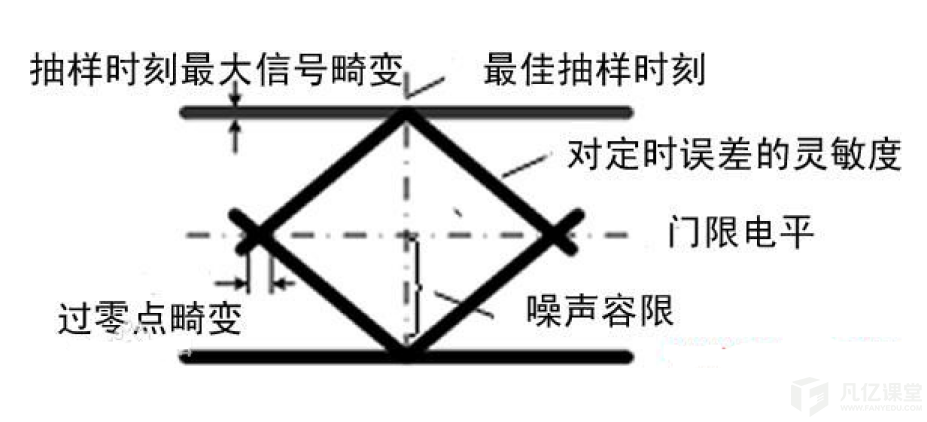

反射(reflection)和我们所熟悉的光经过不连续的介质时都会有部分能量反射回来一样,都是信号在传输线上的回波现象。此时信号功率没有全部传输到负载处,有一部分被反射回来现象。

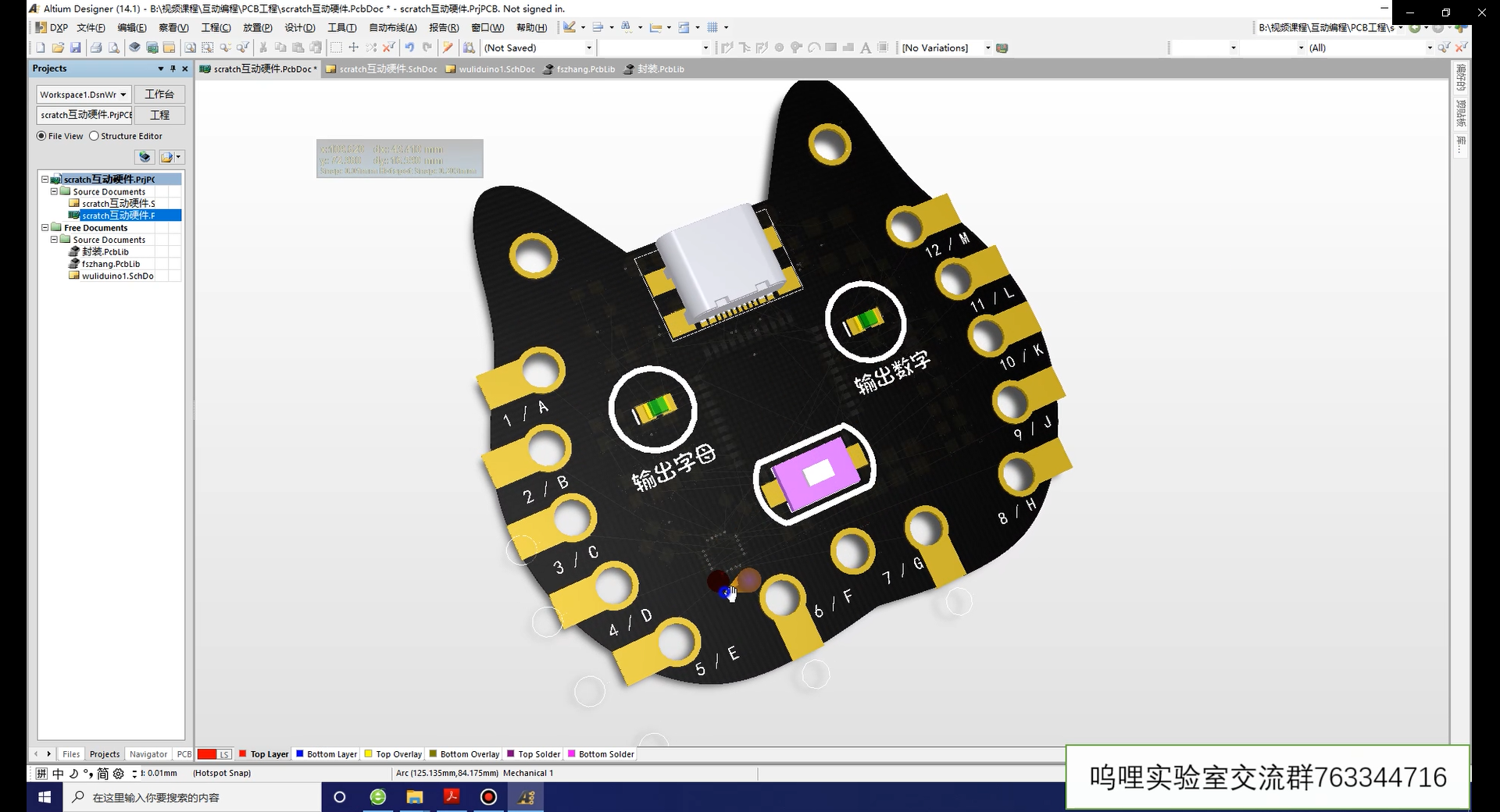

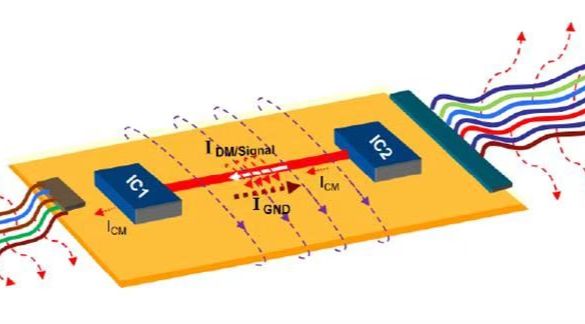

对这个就是一个信号反射模型喔,在高速的PCB中导线必须等效为传输线,按照传输线理论,如果源端与负载端具有相同的阻抗,反射就不会发生了。如果二者阻抗不匹配就会引起反射,负载会将一部分电压反射回源端。根据负载阻抗和源阻抗的关系大小不同,反射电压可能为正,也可能为负。如果反射信号很强,叠加在原信号上,很可能改变逻辑状态,导致接收数据错误。如果反射发生在时钟信号上可能引起时钟沿不单调,进而引起误触发。

Cadence Allegro 17.2反射仿真分析流程中怎么进行信号分析?

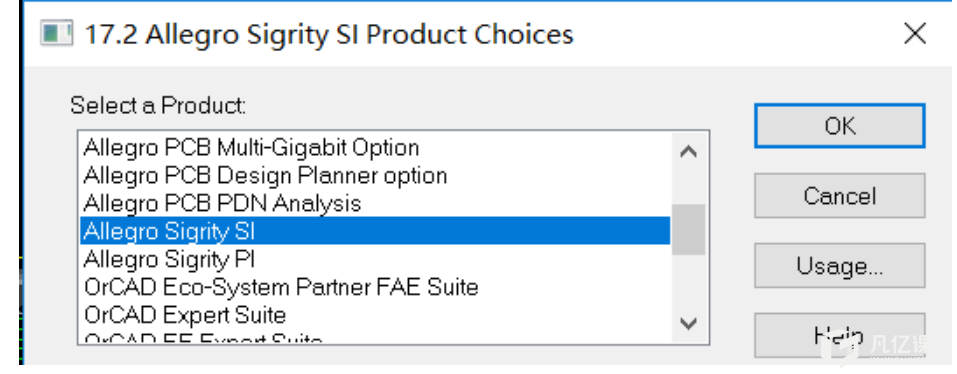

【1】Cadence Allegro 17.2启动后选择Allegro Sigrity SI产品就可以启动Sigrity信号完整性分析的产品平台工具。

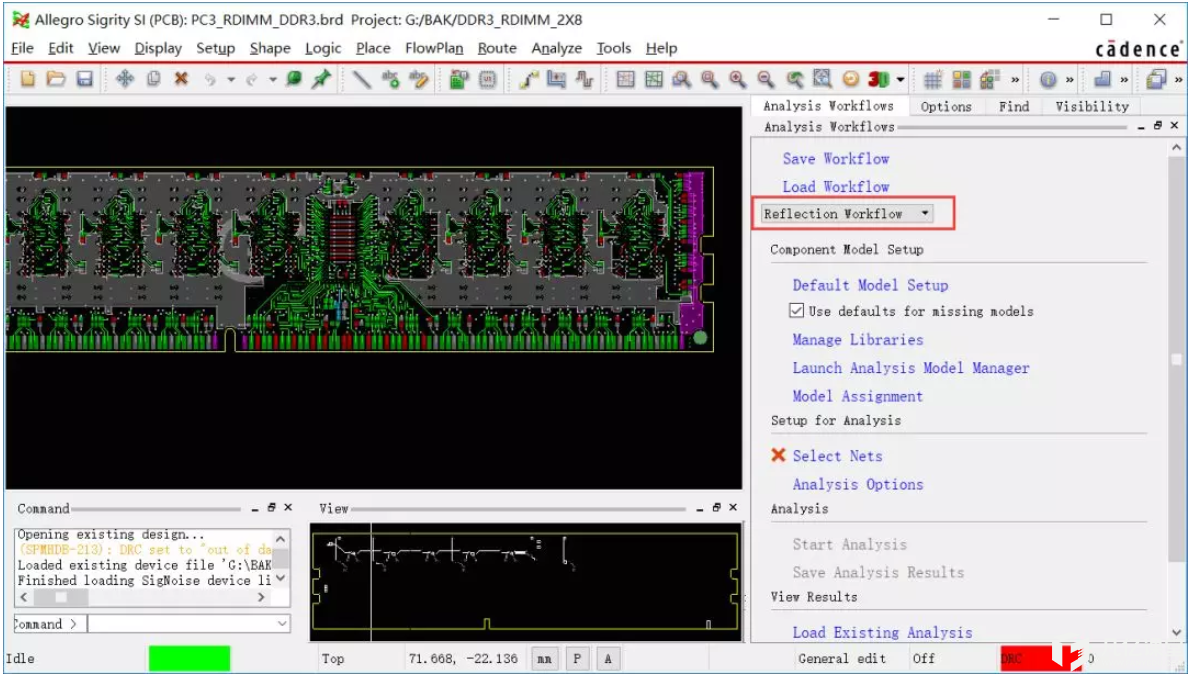

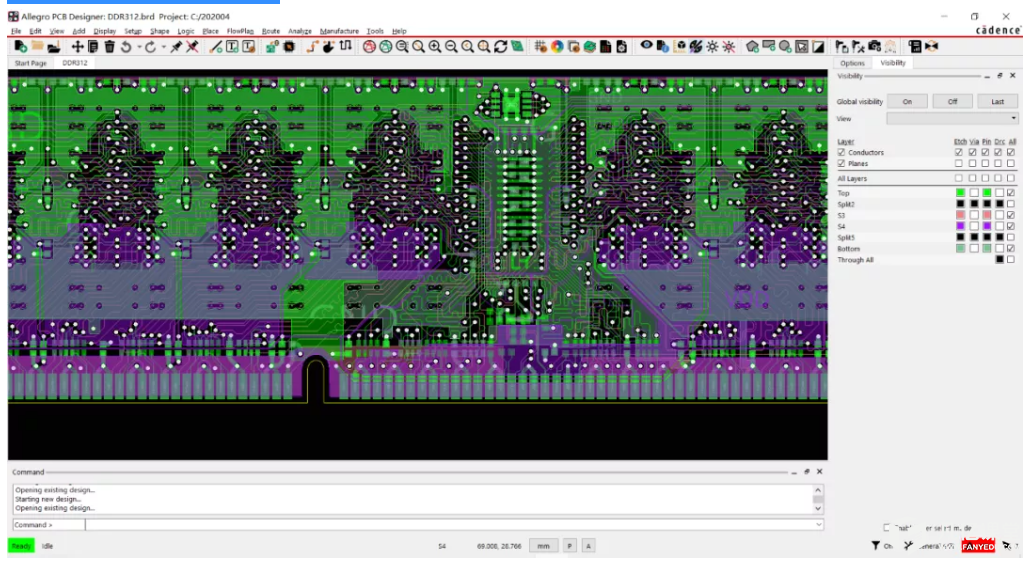

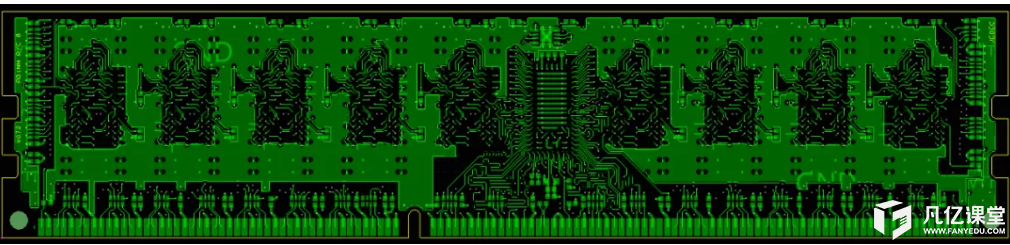

【2】Allegro Sigrity SI产品启动后,需要选择用于进行反射分析的实例文件,今天我和小伙伴一起使用一个PC3_RDIMM_DDR3的内存条实例文件进行分析。当加载实例文件完成以后,选择Analyze—Analysis Workflow中的Reflection Workflow即可进入信号反射分析的流程。

【3】需要提取网络所涉及到的驱动源或接收源赋予IO的模型(或者说是匹配上模型,这个模型就是IBIS或者SPICE的模型),Default IO Cell Models是Allegro 17.2默认给出的单IO和差分对IO模型文件。当勾选use defaults for missing models复选框后,Allegro 17.2会将没有赋予模型的网络IO模型自动匹配到这些默认的模型上。(一般情况下,默认模型文件不建议修改)

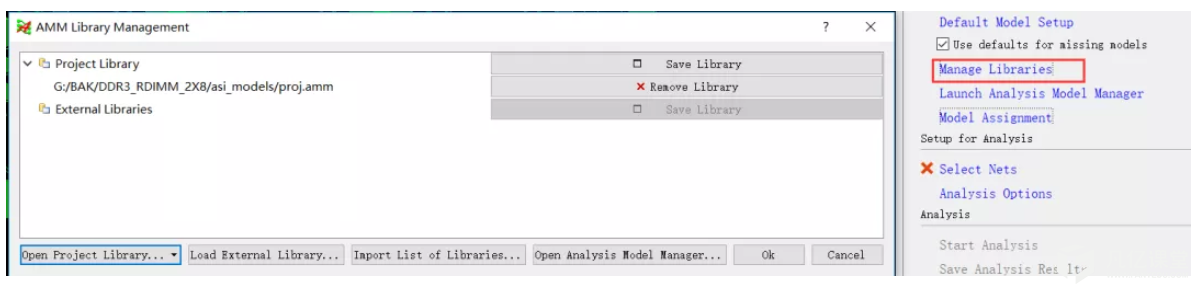

【4】Manage Libraries用来做模型库的路径设置,可以配置项目的库路径也可以用来设置集中的外部库路径配置。Project Library 默认情况下自动指向当前PCB文件存在的路径下,也支持进行库路径编辑修改。External Libraries用来配置系统外部集中库路径位置,比如可以配置集中的电容库路径,或者其他所需要用到仿真库路径。(路径建议不出现中文为宜)

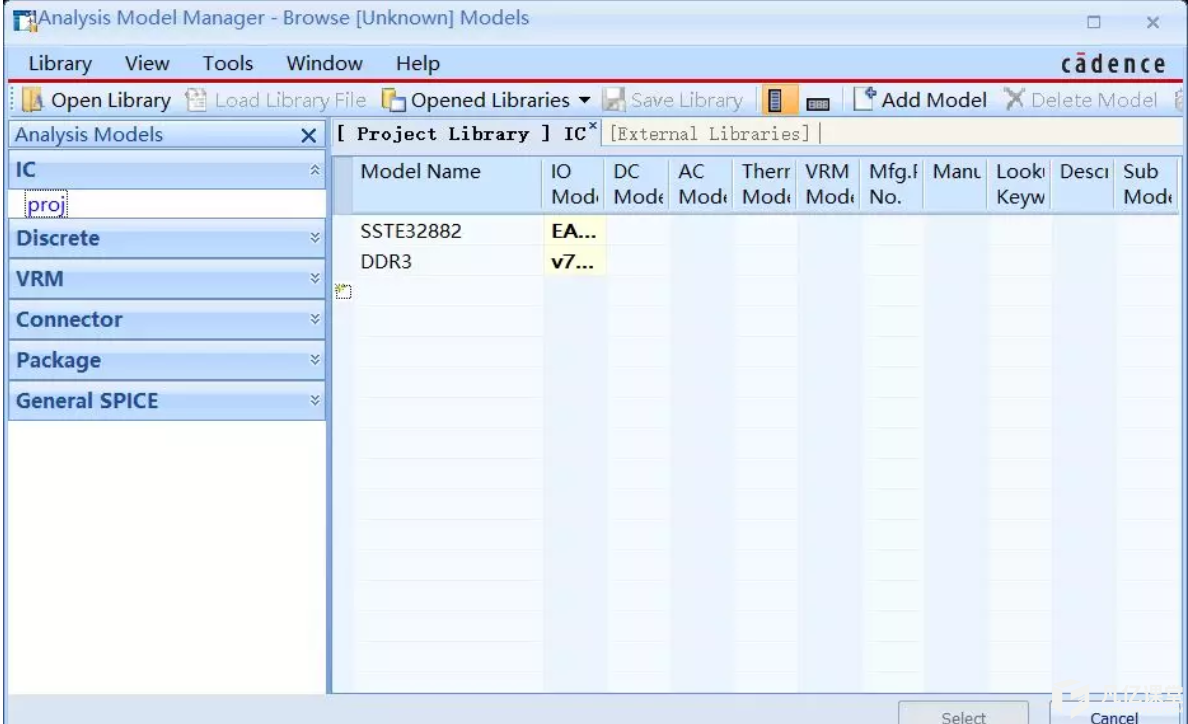

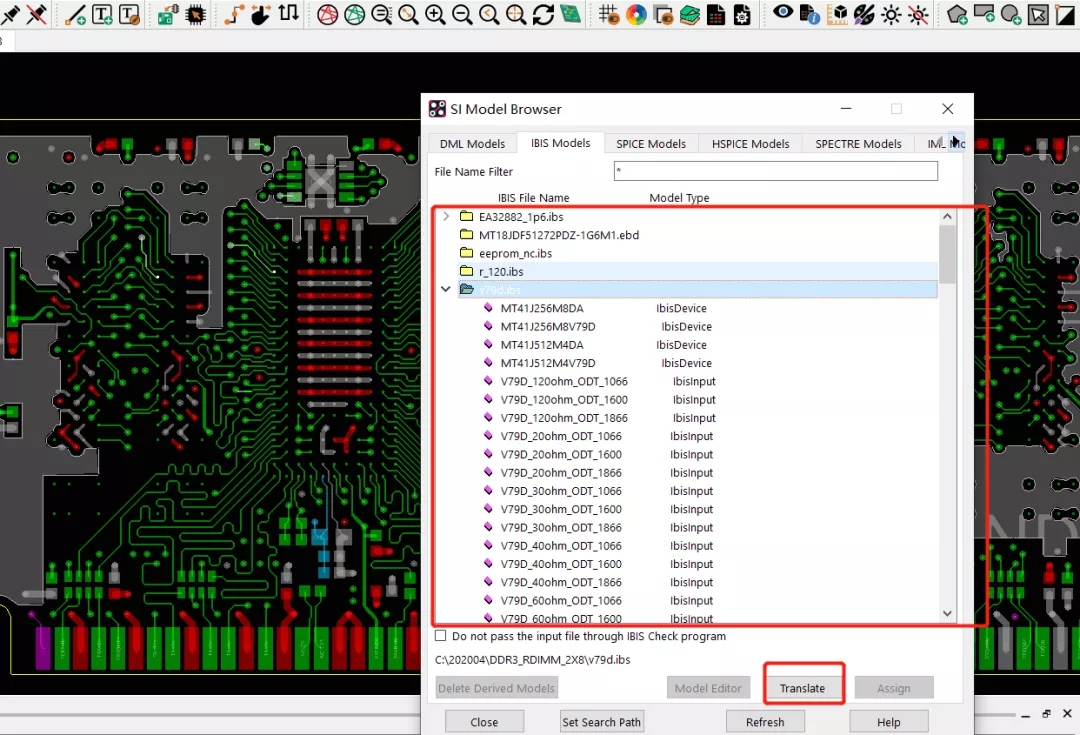

【5】Launch Analysis Model Manager用来添加所需要的模型库。比如可以通过手动方式来添加浏览项目的库路径和模型文件等。

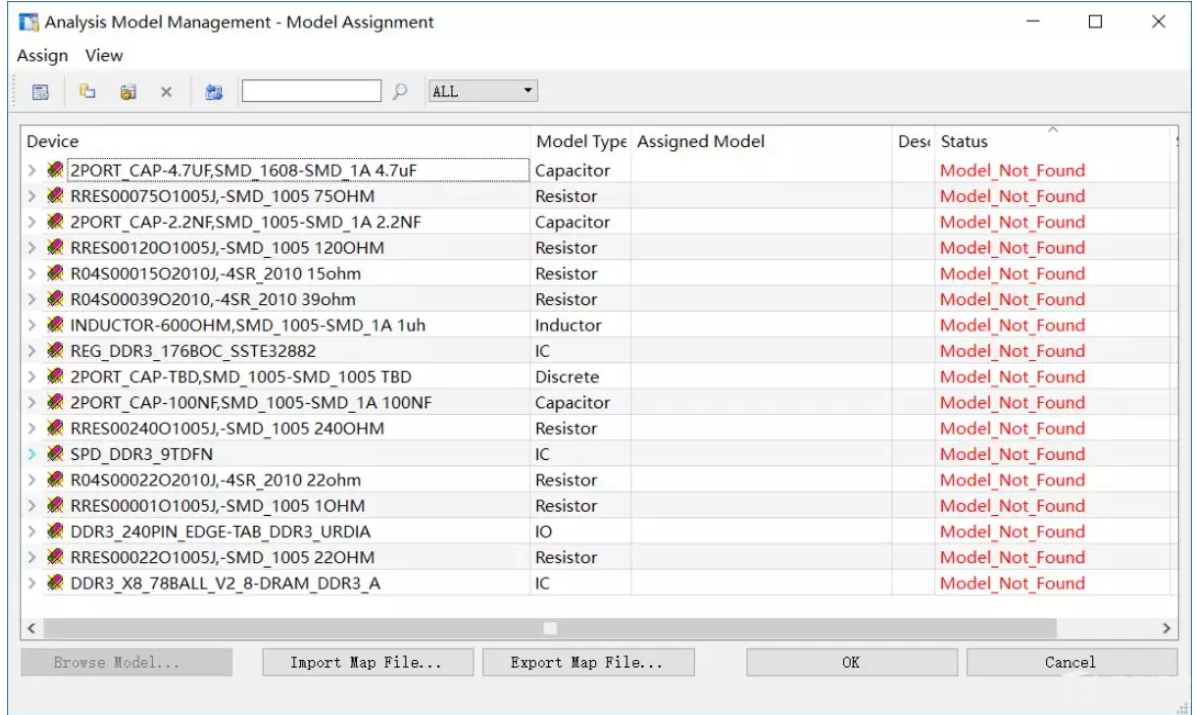

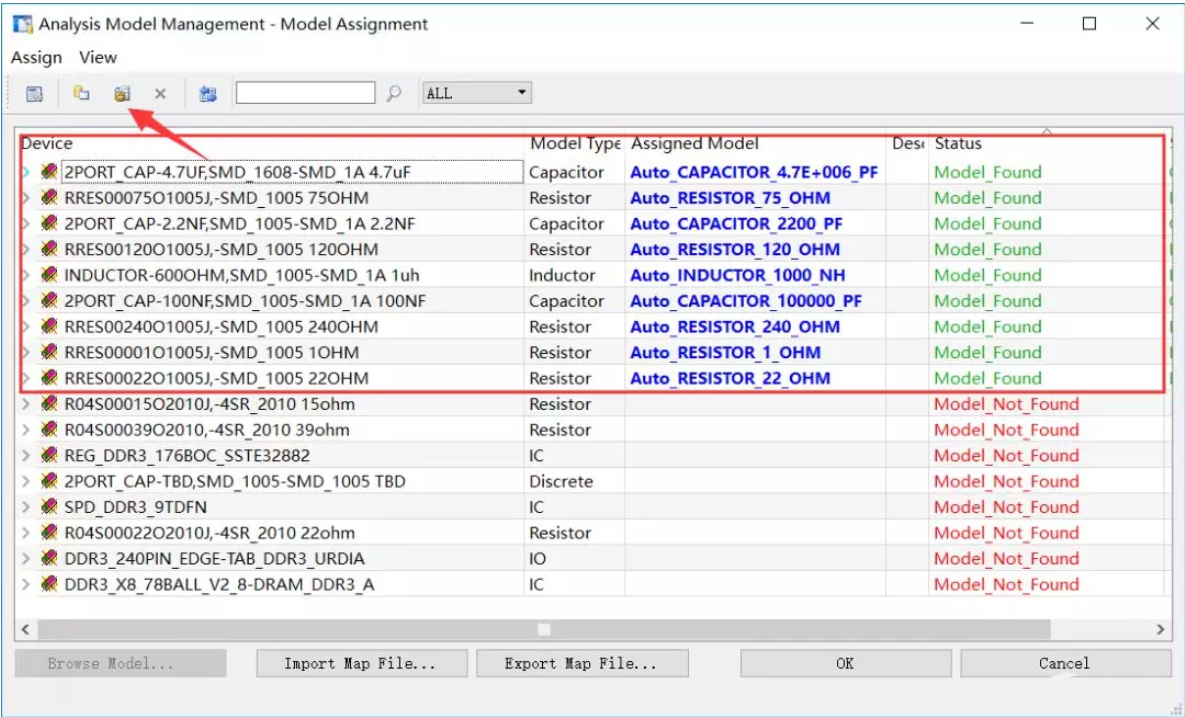

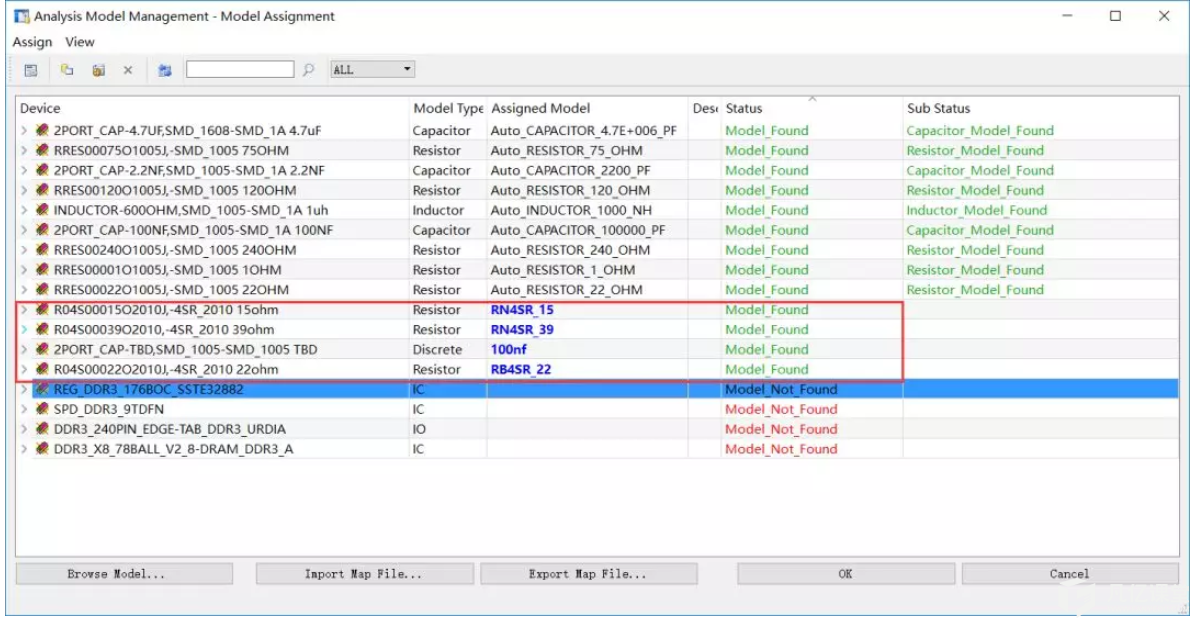

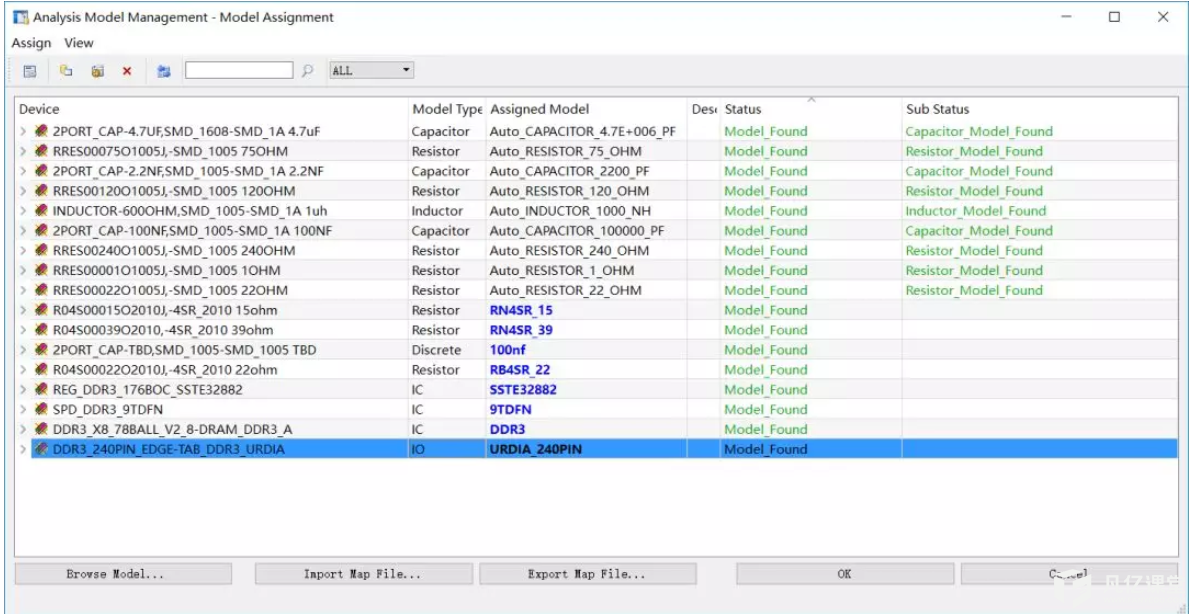

【6】Model Assignment用来分配模型,在弹出的窗口中可以对当前实例文件中的所有器件模型进行预览和分配。

【7】点击Auto Generate Models Allegro 17.2会根据设置的Project Library和External Libraries自动匹配相互关联的模型文件,比如常用的R,L,C无源器件。当匹配完成以后,在右侧的Assigned Model栏目中就给出已经匹配完成的器件信息结果。

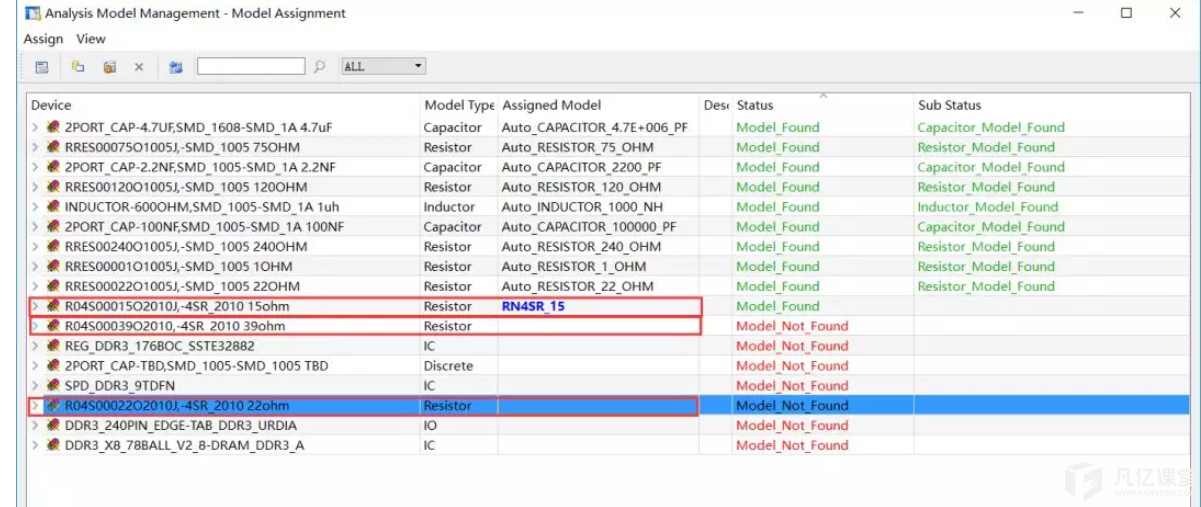

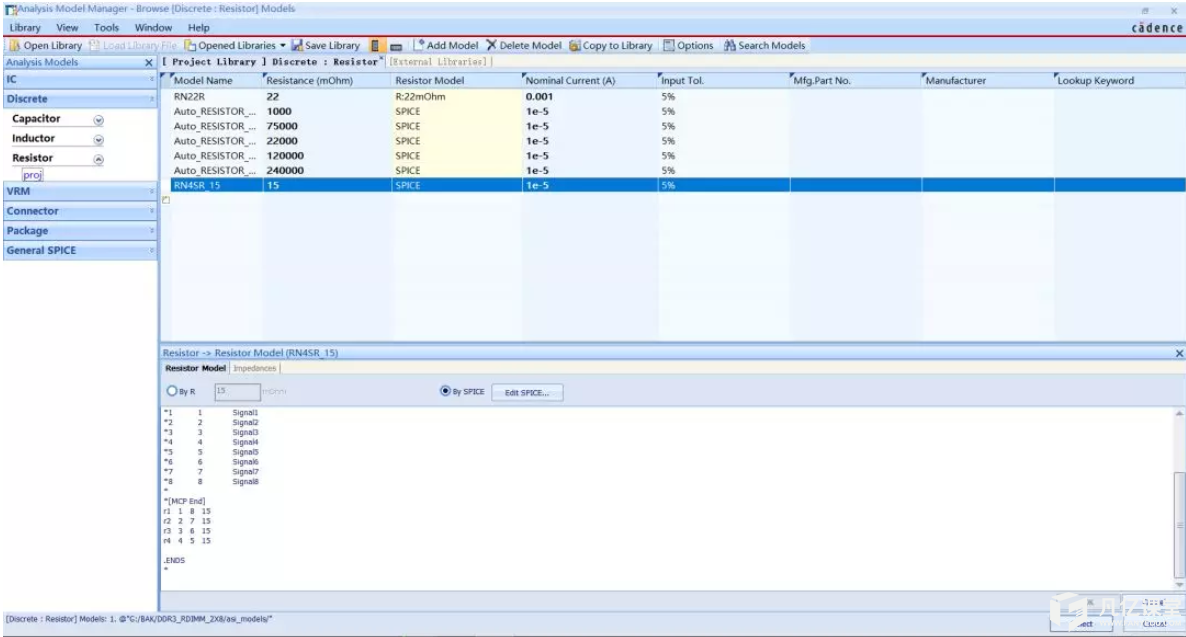

【8】补充其他电阻器件的模型,R04S00015O152110J-4SR_2010_15ohm&39ohm&22ohm这三个器件都是排阻,需要给这三个排阻添加模型文件。分别选择这三个器件以后,选择Assign—Launch analysis models manager命令,在弹出的Analysis Model Manager窗口中新建立模型文件。

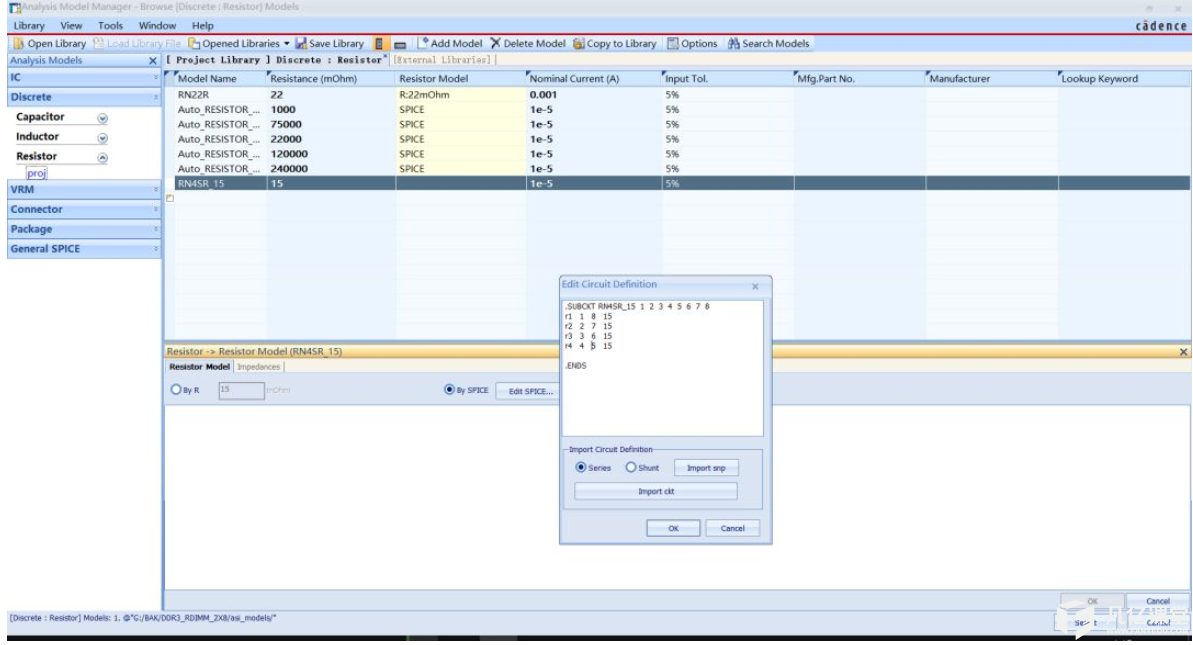

【9】新建立电阻模型RN4SR_15,用SPICE语法建立排阻的模型文件。

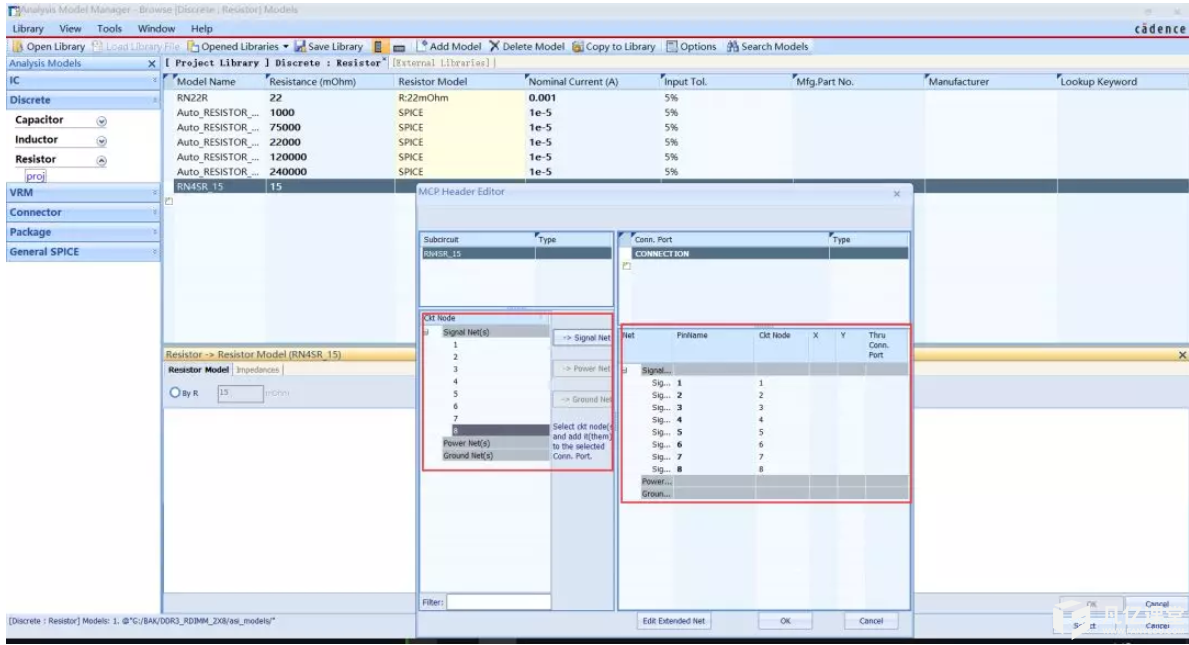

【10】修改排阻的端点 1 2 3 4 5 6 7 8 都为信号类型的网络节点。

【11】修改SPICE模型文件,完成排阻的模型建立。

【12】完成无源器件的模型创建和分配。

【13】同理完成,完其他器件的模型创建和分配。

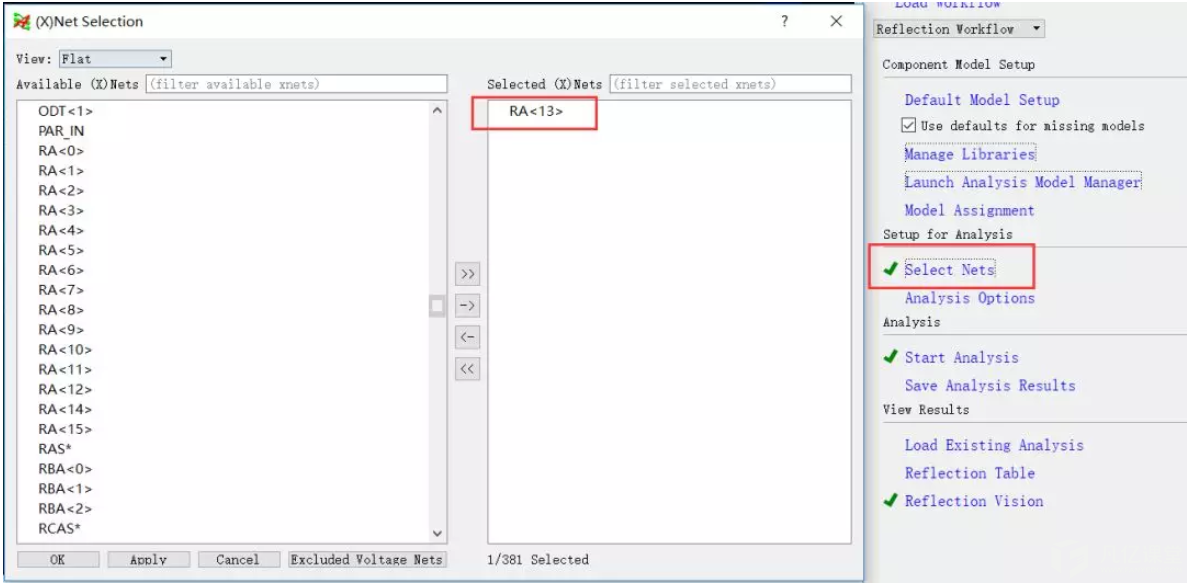

【14】选择需要进行反射仿真分析的网络,比如A

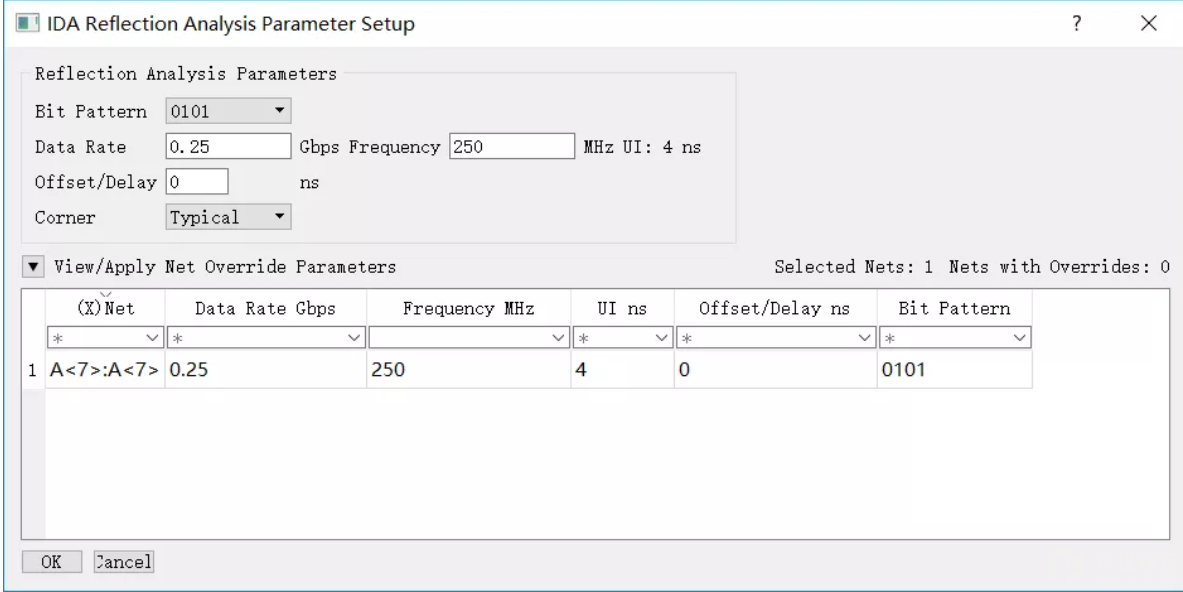

【15】设置仿真参数。

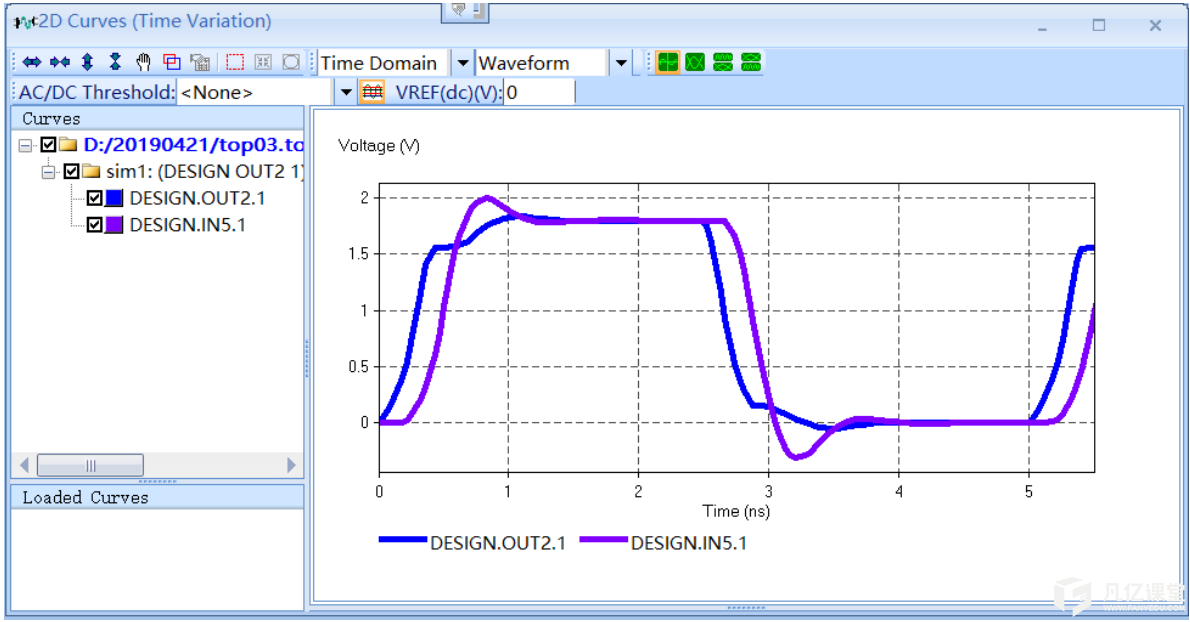

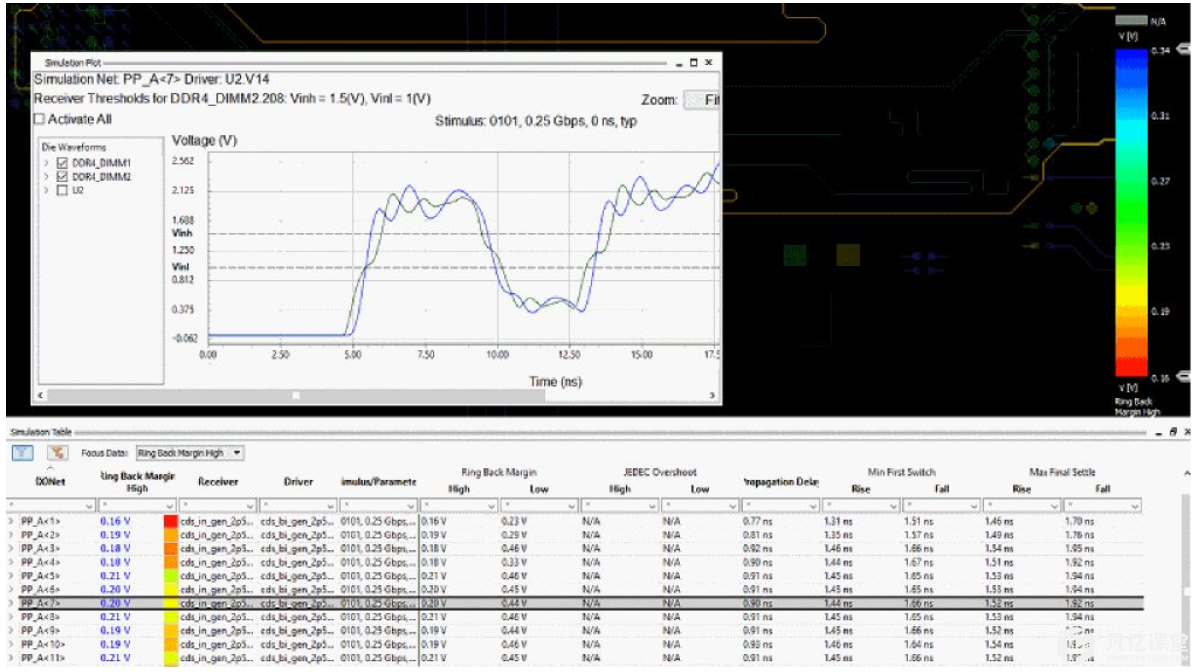

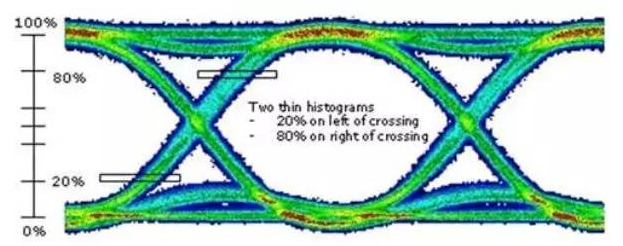

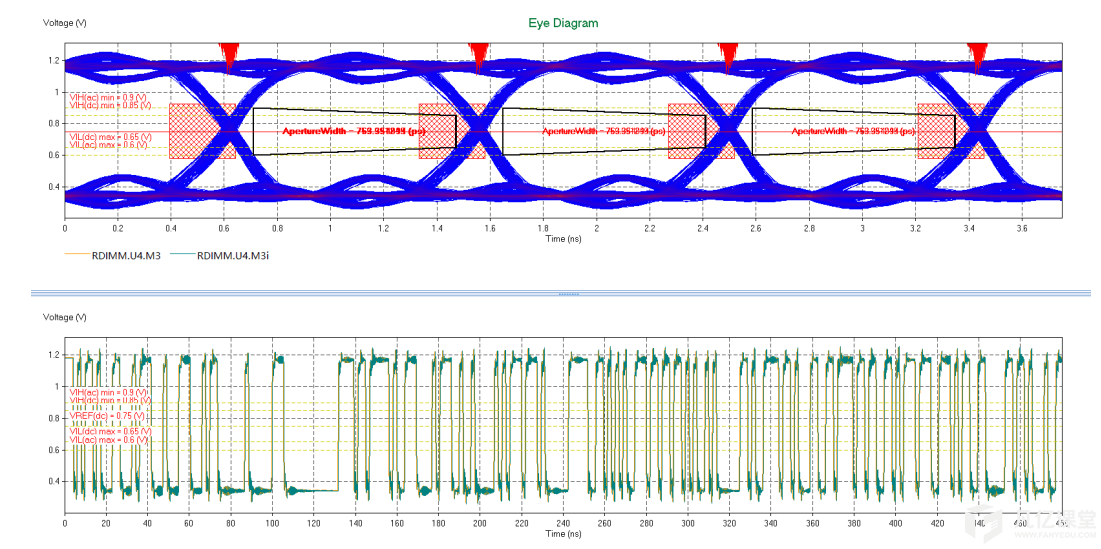

【16】选择Start Analysis即可开始反射信号仿真,等待仿真完成以后结果就可以显示在出来,图下图所示。结果显示的表格里面给出了具体的信号的发射和接收端的信号时域图,从图中可以看到信号的发射端和接收端的信号情况。也通过表格的形式给出了信号自动测量的结果,其中包括信号过冲,信号的下冲,信号的最小高电平余量,最小低电平余量,信号的VERF电压等参数。

右侧的窗口中可以通过高亮的方式显示出信号传输链路所在的位置,通过观察色卡的颜色可以看到信号在整个传输链路里面位置情况,那些地方存在比较大的反射情况,反射最严重的地方发生在传输链路的那些地方等。

通过这样直观的手段来对PCB信号传输链路中存在的反射问题显示出来,以便于工程师能够更加准确的来解决信号这些信号反射的问题,以便于提高信号的质量。

通过上面的学习让我们看到了全新的Cadence Allegro 17.2 信号反射仿真的分析方法,可以允许工程师在Allegro Sigrity SI的环境下对PCB存在的反射问题进行更加直观的检查,发现和修改。这样做成为减少潜在信号反射设计问题的重要方法之一,对于提升设计效率以及设计的准确性是有很大帮助。阅读完这篇文章的小伙伴可以自己去试一试这个新功能,让自己的设计做到心中有数,胸有成竹。

声明:本文来源于耀创深圳 旅行的苏西,版权归原作者所有。

如涉及版权或对版权有所疑问,请第一时间与我们联系

扫码关注

扫码关注

![电子设计:从PROM到FPGA[零基础学FPGA设计-理解硬件编程思想]](https://api.fanyedu.com/uploads/image/48/73f5e6b538c04ceb976518793db794.png)