信号完整性测试(SI)是硬件测试的常见内容之一,也是通信/无线工程师需要重点了解的基础内容之一,但有很多小白遇见SI问题却不知道如何解决,所以本文将重点分享常见的信号完整性测试(SI)问题及解答内容。

1、反射产生的原因

一般来说,反射产生的原因大致上有组开始配、桩线、过孔、其它连接的不连续性等。

2、串扰产生的原因

串扰产生的原因有传输线之间的耦合、过孔之间的耦合、传输线与平面之间的耦合、两个平面之间的耦合。

3、电源/地噪音产生的原因

①SSO(全称:simultaneous switching output)驱动同步输出对电源或者地的寄生效应,也叫作对地反弹。

②SSN(全称:simultaneous switching noise)同步开关噪音或电流变化噪音。

除此之外还有两个问题会导致信号波形的失真:

①EMC(全称:electromagnetic compatibility)电磁兼容

②EMI(全称:electromagnetic interference)电磁干扰

4、信号完整性问题的影响

当信号完整性存在问题或者系统的噪音余度要求没有达到满足的时候,输入信号在开关接收端到达最小高电平前就或者到达最小低电平前就开始变形,输入信号在静态接收端到达最高低电平前就开始上升或者在到达最小高电平前就开始下降,电源电压的波动也会扰乱锁存中的数据,于是会导致逻辑错误,数据信号变弱,开关错误,甚至导致系统失效。

5、产生SI问题的地方

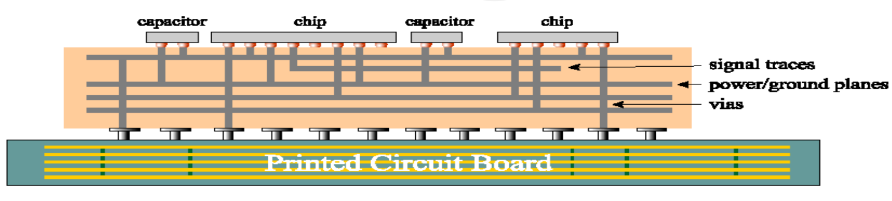

典型数字系统环境流程:

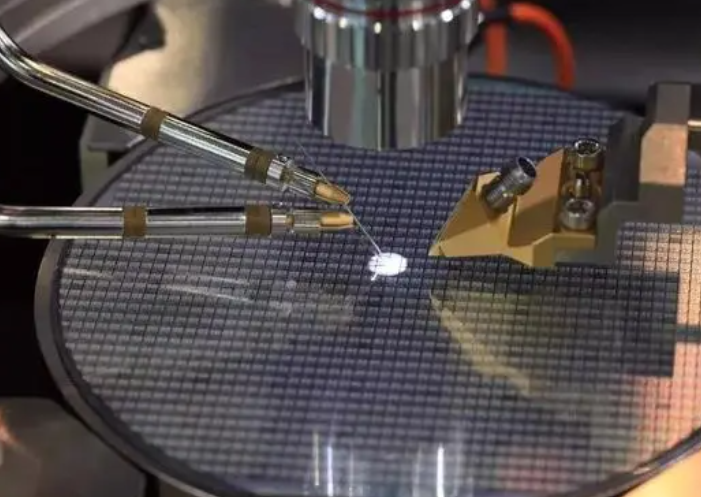

硅片驱动——引线接合器——芯片封装——芯片封装焊接点——PCB——另一个系统器件

源终端,传输过程,接收端。我们最关注的是信号在传输过程中的完整性。

电子工艺的趋向是不断加快芯片运行的速度以及不断提高芯片的集成度从而将芯片的性能推向极限。目前个人电脑中的最快时钟频率已经达到GHz的范围,它的上升时间已经小于200ps,目前看来数字信号的最快频率可以达到10GHz。随着制造工艺的不断发展,逻辑门的长度从20世纪60年代的50us发展到21世纪初的0.18us,目前的流行工艺是0.13us,成熟工艺可以做到0.09us和65ns。

芯片的时钟频率几乎每过18个月就翻一翻;逻辑门的固有延迟已经减小到几十个ps,但是封装设计技术还非常落后,就当前的工艺来说,封装上的连接延迟直接支配着系统时序余度也成为高频系统设计领域的瓶颈。所以目前我们公认的说法是:封装的性能成为整个系统性能的最主要制约因素之一。

扫码关注

扫码关注