一个layout工程师学习信号完整性之路

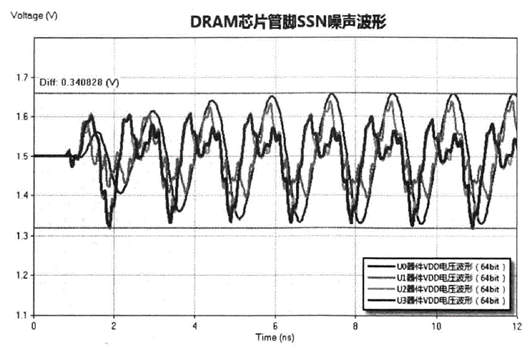

造成电源完整性的问题有很多,之前也和大家分享过一些。但这些问题都不是独立的,他们之间的原理是互通,可能解决了这个问题另外一个问题就解决了。可能对于这个SSN在我们实际的LAYOUT或者测试工程师接触的较少,因为我们平常对于电源比较关心的是直流压降和交流阻抗,测试方面可能就是纹波之类的。本人是在无意间接触到了这个概念,所以也从仿真中和查看书籍中简单总结一下,如下:

一、同步开关噪声定义

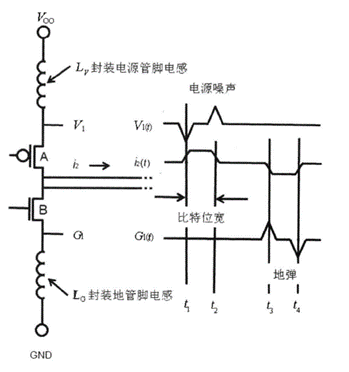

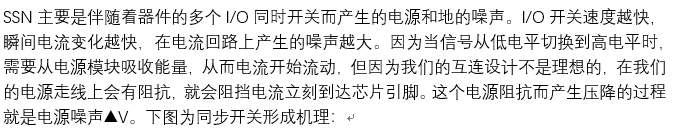

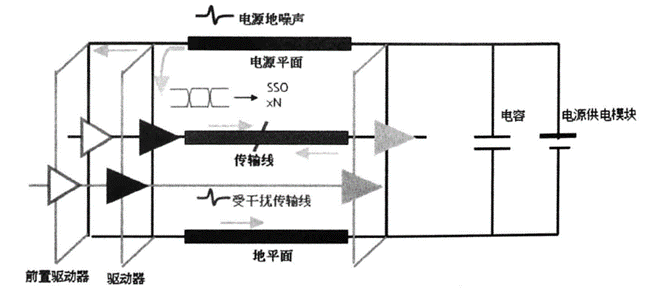

二、同步开关噪声的分析

三、减小SSN的方法

1)减小信号的电源和地平面的阻抗

2)减小电源和地的回路电感

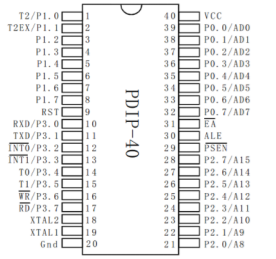

3)合理分配芯片的信号、电源和地引脚的数量比值

4)在芯片电源和地引脚附件添加合理的去耦电容

以上资料主要是本人在仿真流程中和网络搜索整理而成,

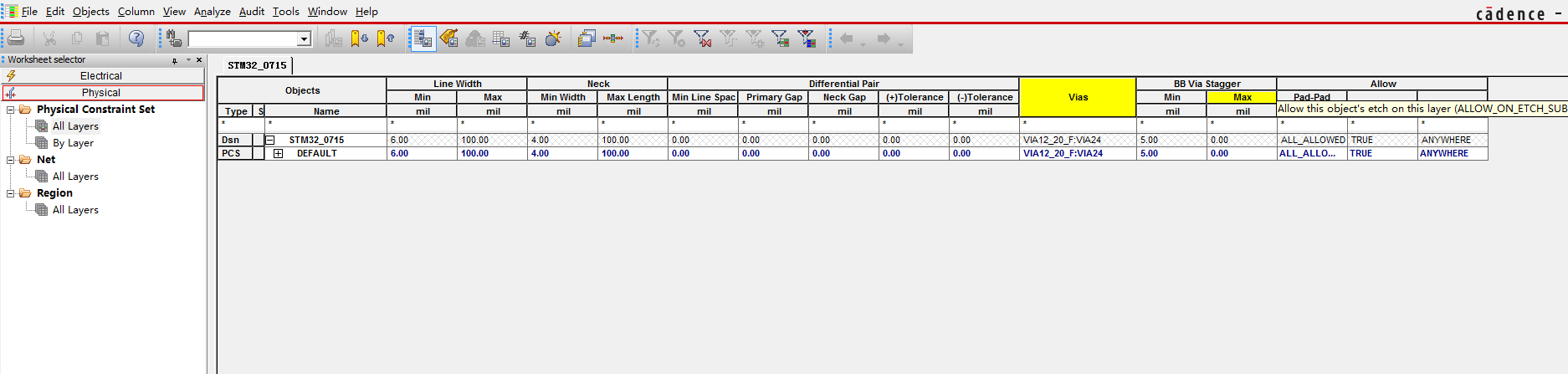

同时也参考了《Cadence 高速电路设计》

如有雷同或错误,希望各位大神留言指正,感谢!!!

扫码关注

扫码关注

![电子设计:如何才算学会了FPGA?[零基础学FPGA设计-理解硬件编程思想]](https://api.fanyedu.com/uploads/image/66/620776fd2b3ad7be7fe4984c6c80a5.png)