MOS晶体管在电子电路中是非常关键的电子部件,也是小白初学集成电路设计的重点内容之一,今天我们来谈谈MOS晶体管的电容特性。

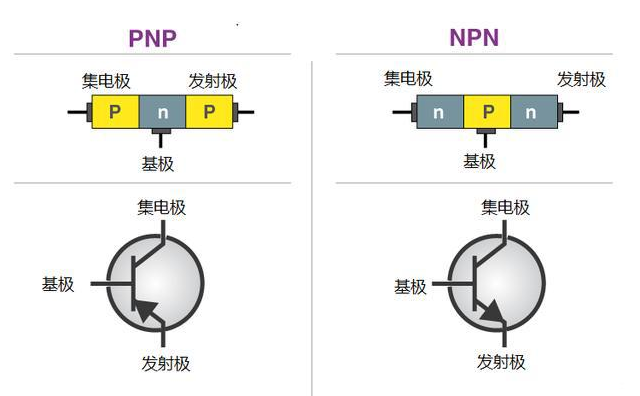

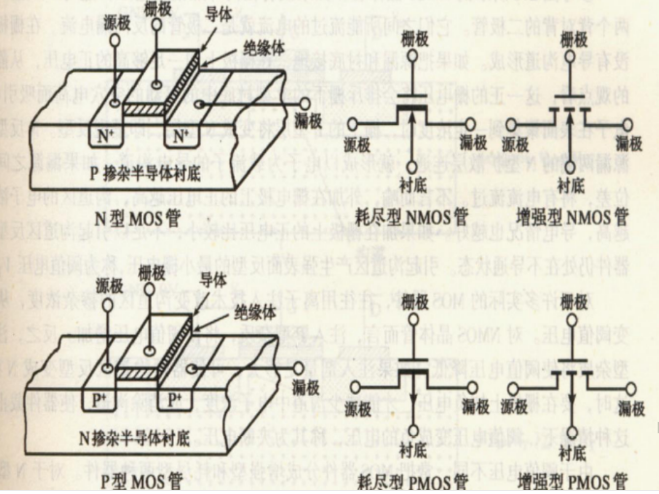

常见的MOS晶体管主要分为N型MOS管和P型MOS管,它们的基本结构和电路符号如图所示:

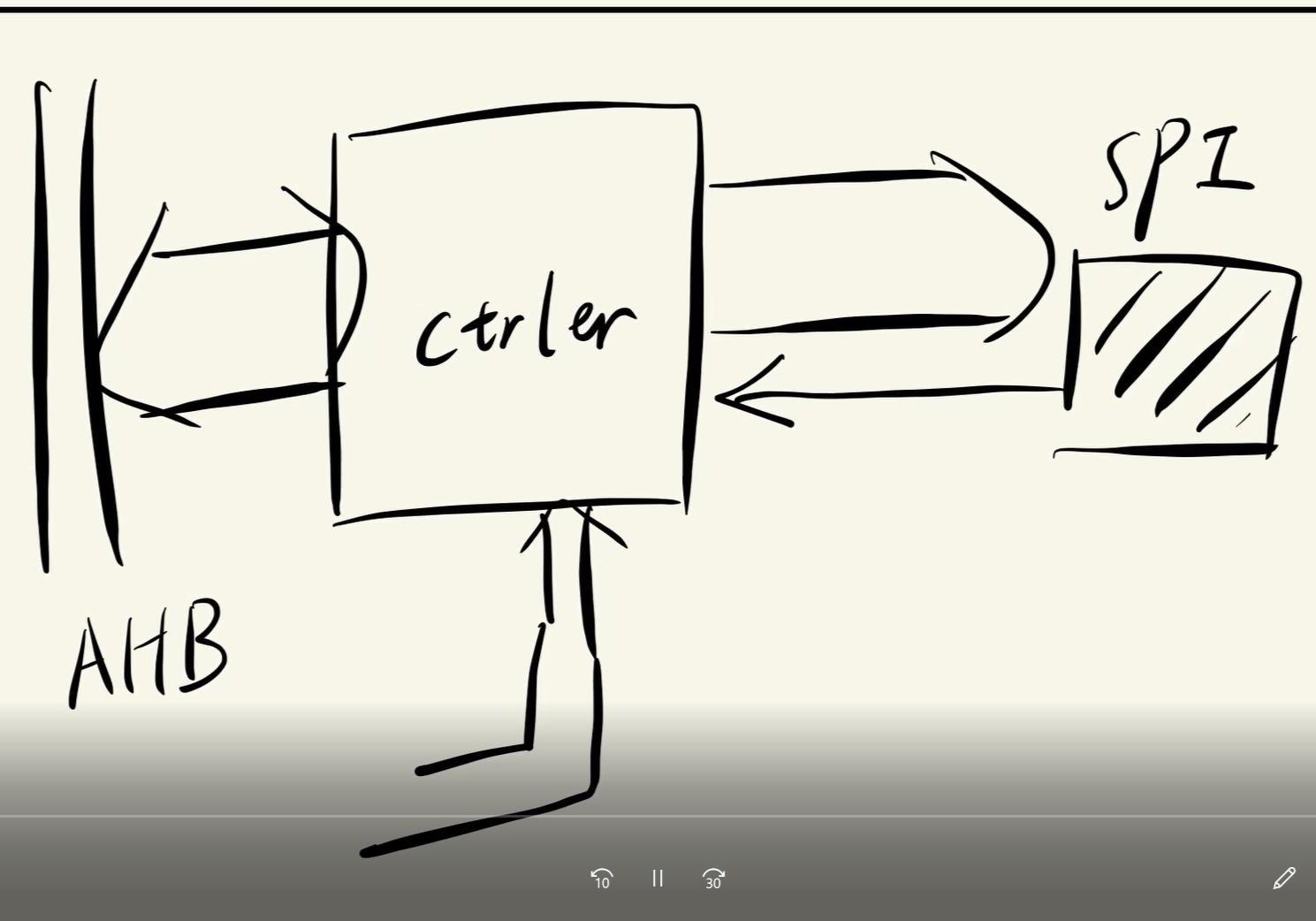

MOS晶体管的伏安特性:电容结构

当栅极不加电压或加负电压时,栅极下面的区域保持P型导电类型,漏和源之间等效于一对背靠背的二极管,当漏源电极之间加上电压时,除了PN结的漏电流之外,不会有更多电流形成。

当栅极上的正电压不断升高时,P型区内的空穴被不断地排斥到衬底方向。当栅极上的电压超过阈值电压VT,在栅极下的P型区域内就形成电子分布,建立起反型层,即N型层,把同为N型的源、漏扩散区连城一体,形成从漏极到源极的导电沟道。这时,栅极电压所感应的电荷Q为

Q=CVge

式中Vge是栅极有效控制电压

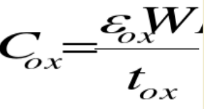

1、当Vgs<0时,栅极上的负电荷吸引了P型衬底中的多数载流子——空穴,使他们聚集在Si表面上,这些正电荷在数量上与栅极上的负电荷相等,于是在Si表面和栅极之间,形成了SiO为介质的平板电容器,其容量为:

tox是厚度,单位是cm。

2、当电容Vgs>0时,栅极上的正电荷排斥了Si中的空穴,在栅极下面的Si表面上,形成了一个耗尽区。

耗尽区中没有可以自由活动的载流子,只有空穴被赶走后剩下的固定的负电荷,这些束缚电荷是分布在厚度为Xp的整个耗尽区内,而栅极上的正电荷则集中在山鸡表面,这说明了MOS电容器可以看成两个电容器的串联。

Cox:以SiO为介质的电容器

Csi:以耗尽层为介质的电容器

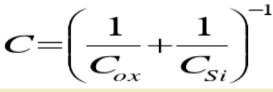

总电容C为:

需要注意的是总电容C比原来的Cox要小些。

3、随着Vgs的增大,排斥掉更多的空穴,耗尽层厚Xp增大,耗尽层上的电压降就增大,因而耗尽层电容Csi就减小,耗尽层上的电压降的增大,实际上就意味着Si表面电位势垒的下降,意味着Si表面能级的下降。

一旦Si表面能级下降到P型衬底的费米能级,Si表面的半导体呈中性,这时在Si表面,电子浓度与空穴浓度相等,成为本征半导体。

扫码关注

扫码关注