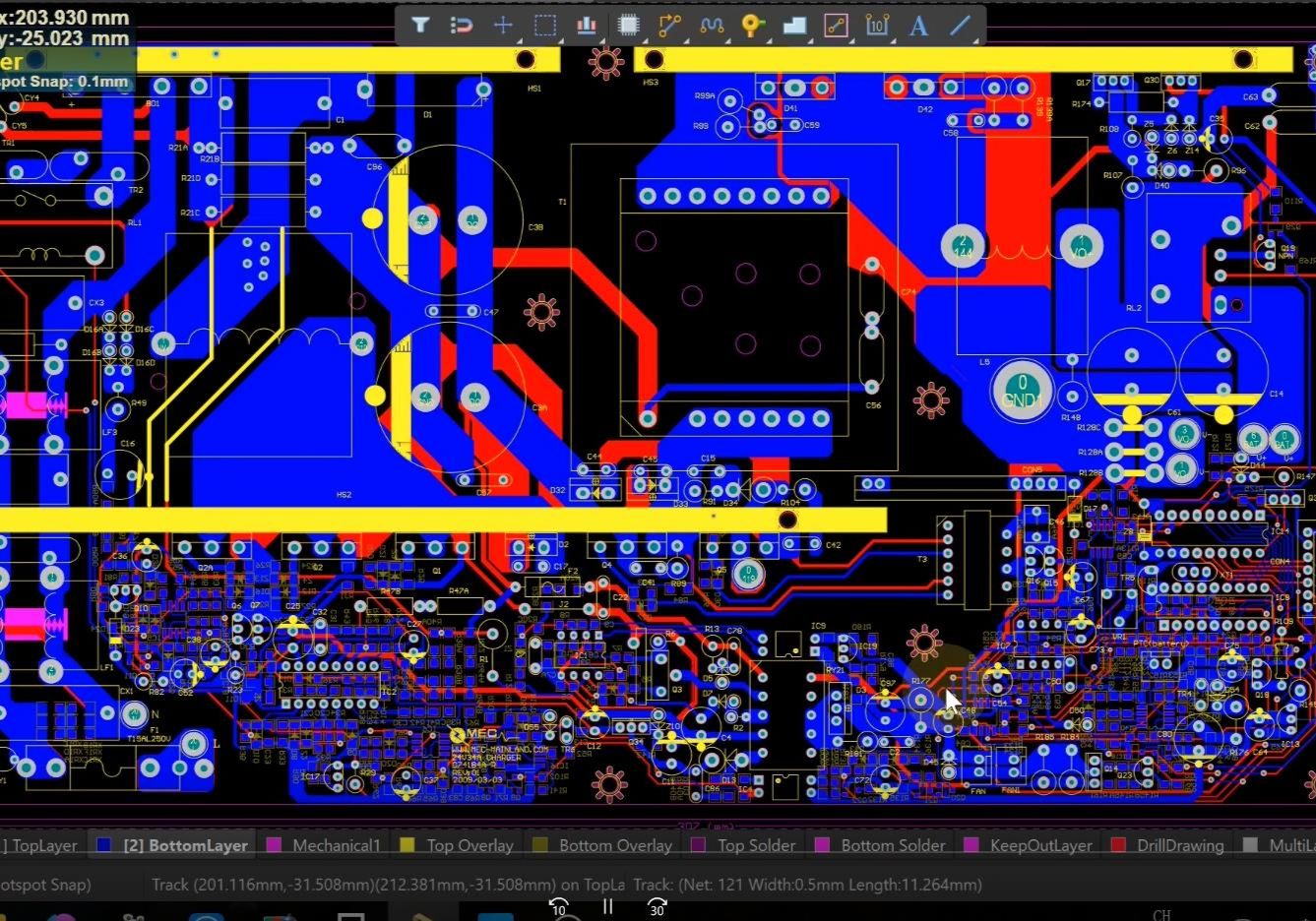

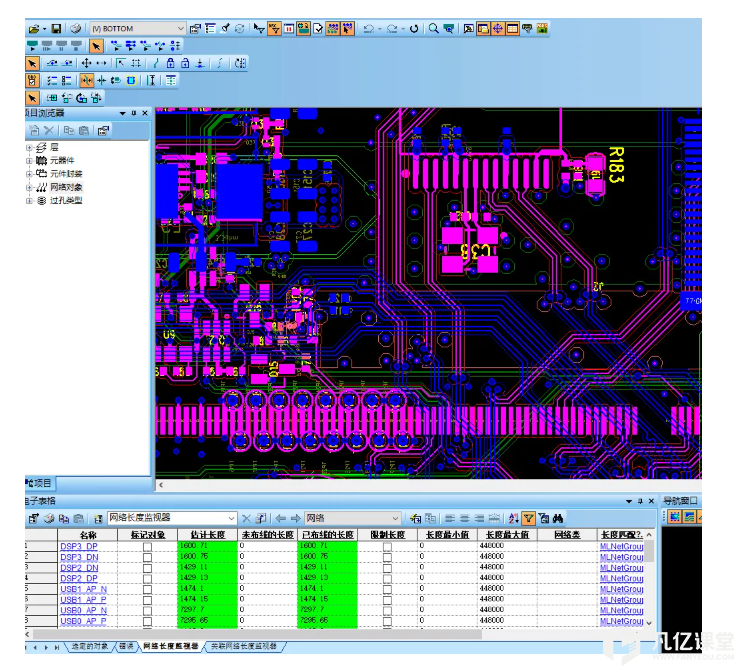

今天在设计PCB时,遇到了5对差分线。结果我花了整整一天的时间,都是在捣鼓这5对差分线。有人会问,花一天的时间去设计5对差分线,这工作效率太低了吧。人家layout工程师,三两下就可以搞定了。

确实,layout工程师完成这点工作就是一支烟,一个厕所的事情。但是,layout工程师一般只管完成走线的事情,其他要考虑的事情是由我们硬件工程师来完成的。比如,layout工程师把pcb设计完成后,就要由我们硬件工程师来检查,来评审。如果我们硬件工程师检查没有问题,发出去打板,之后调试发现问题,就是硬件工程师的责任了,由硬件工程师来背锅。

所以,经验越是丰富的硬件工程师在设计PCB,考虑的东西就越多,走一根线都会思考一下,琢磨一下,试图从曾经吃过的苦头,受过的教训,遇到的怪事,背过的锅中找到共同的误区,然后想办法规避,防止相同的错误再次发生。

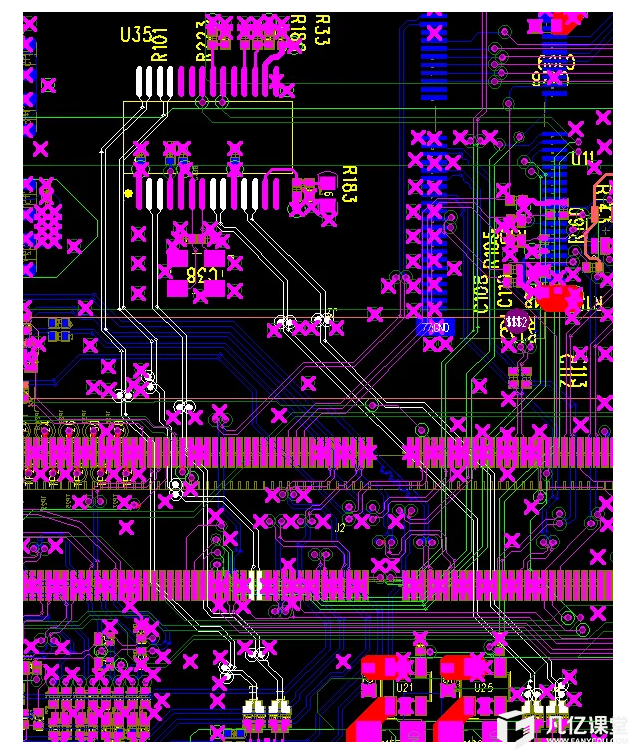

在设计这5对差分线时,虽然很快就已经把它们走通了,但是每检查一次,都会觉得这里处理的不好,那里设计的不妥,总是放心不下,又得重新优化。

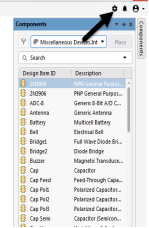

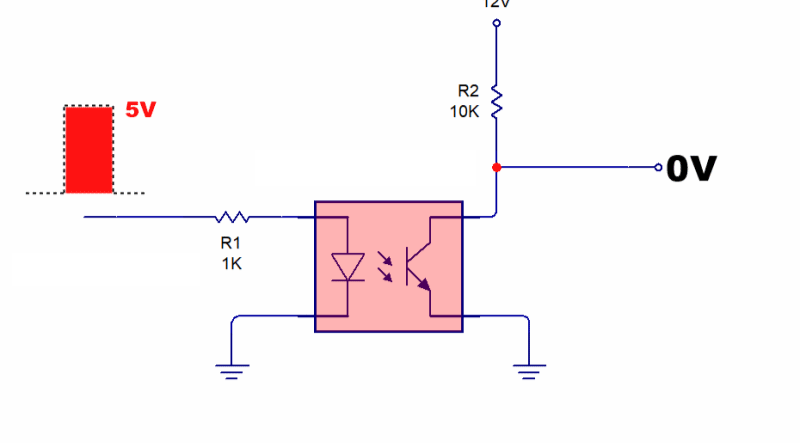

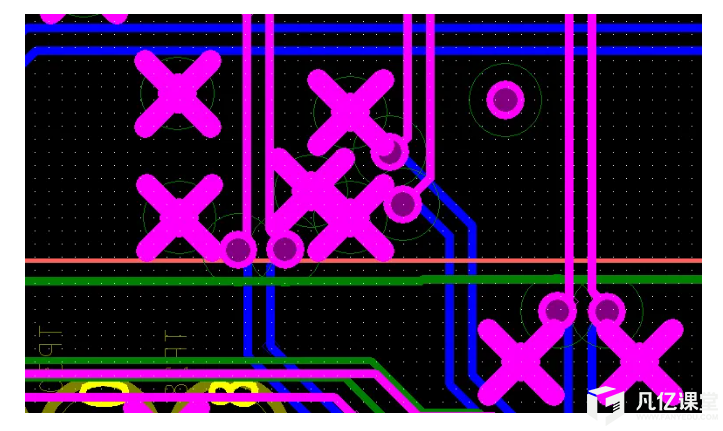

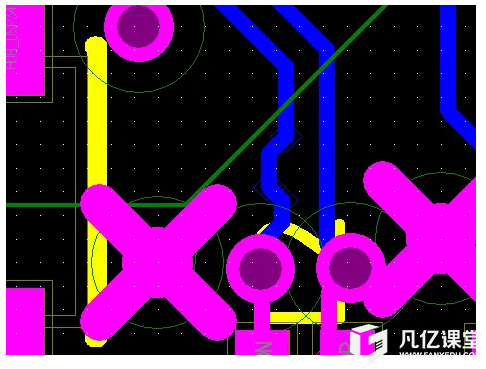

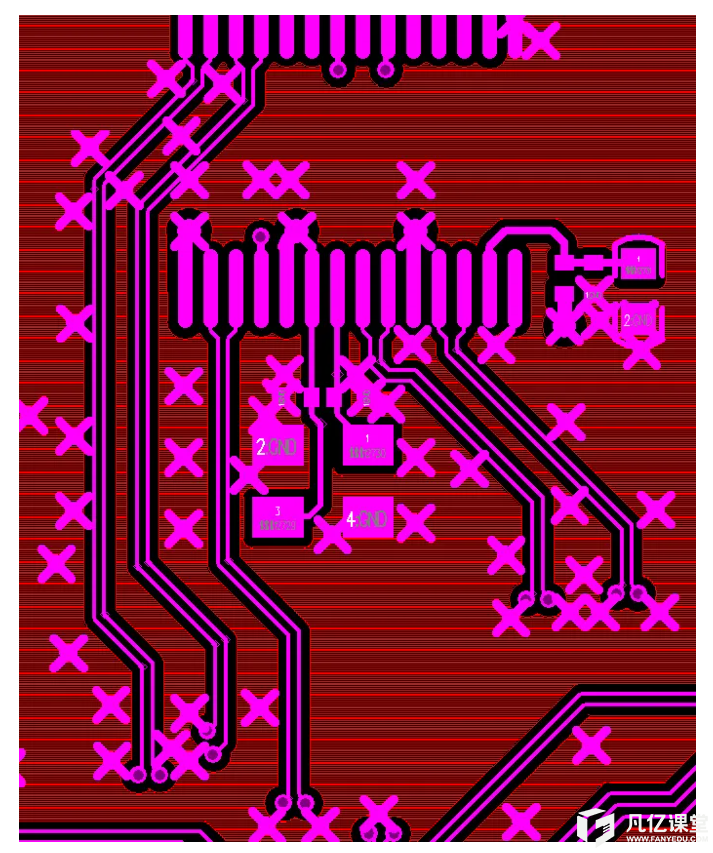

看到换层时,我想到了还没有在换层的两个差分过孔附近分别打一个过孔,然后就重新调整过孔和走线,分别在过孔就近打上一个过孔。

看到等长设计的不够完美,又重新优化,一点一滴调,一丝一毫挪,让等长做到无限接近,才肯罢休。

看到包地做得不够好,又放心不下,又重新调整走线,让包地做好才放心。

就这样,时间过得真快,一天的工作都是在优化这5对差分线。幸好没被老板发现,不然又觉得你啥事没做了。

扫码关注

扫码关注