上一节我们说了下运放的增益,并在文末给出了如何评估运放带宽是否足够的计算方法,但是呢,这个评估带宽的方法,也只是做了一半的工作,还有一个压摆率SR需要评估。

先来看一个具体的例子,压摆率SR造成的问题现象。

例子

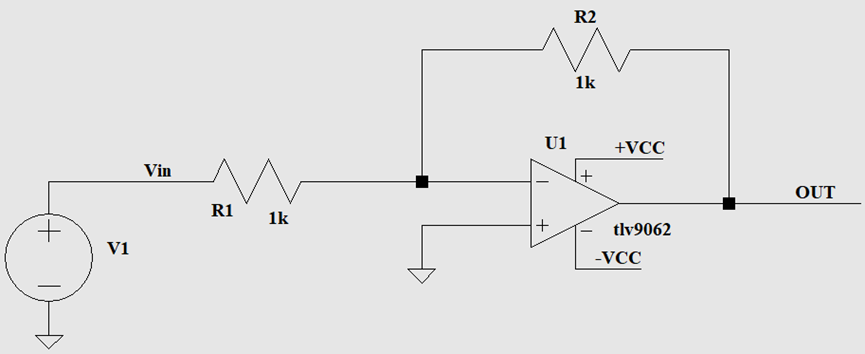

1、使用TI的TLV9061轨至轨运放,构建下面的放大1倍的反相放大电路。

正常情况下,如果我输入1V正弦波,那么输出也是1V正弦波。

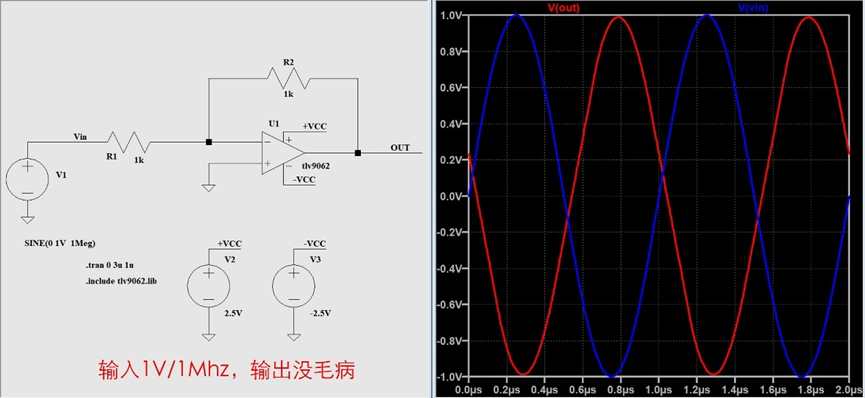

2、现在我们输入1Mhz的1V的正弦波进去运行下:

可以看到,输入1V,输出1V,有一点相移,但是没毛病。

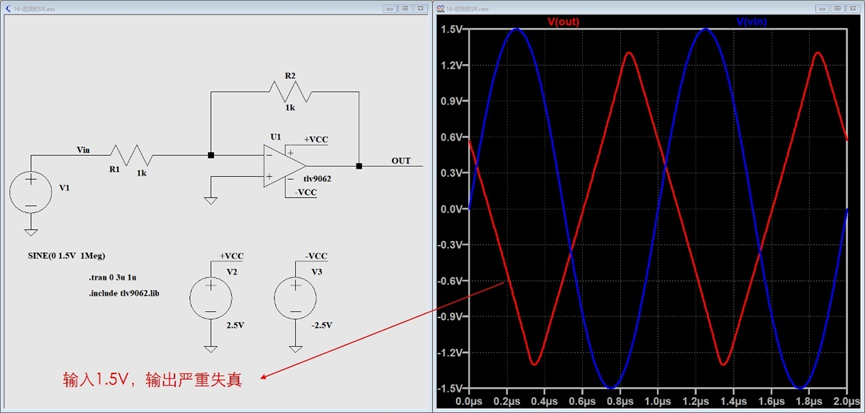

3、将输入信号调大,频率保持1Mhz不变,幅度调到1.5V我们再运行一下:

可以看懂,输入1.5V的时候,输出严重失真,不仅幅度达不到1.5V,波形也酷似三角波。这是为啥嗯?1V输入的时候没问题,1.5V的时候输入有问题,难道是运放仿真模型不对,为非轨至轨?

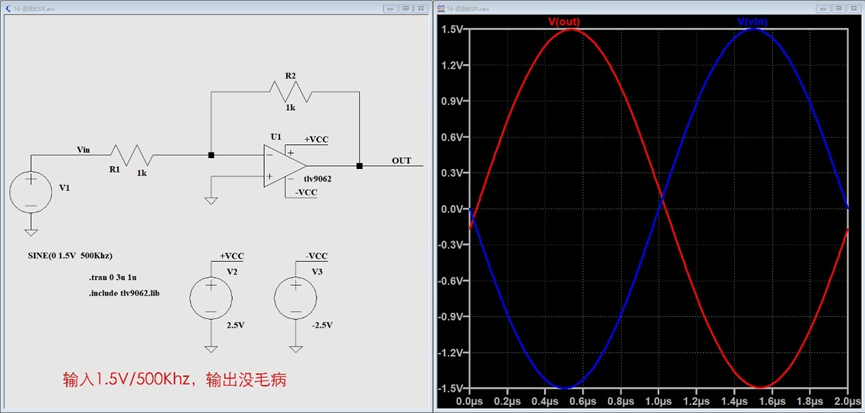

4、我们将输入频率从1Mhz降低到500Khz,幅度保持1.5V再运行下看看:

可以看到,幅度不变,仅仅将频率降低一倍,输出也OK了,说明不是轨至轨的问题,那是带宽的问题吗?

要知道TLV9061的增益带宽积是10Mhz,现在电路放大倍数为1倍,这种情况下理论可以放大10Mhz的信号,现在才1Mhz就不行了?另外1V/1Mhz输入没问题,说明也不是带宽的问题,然后又不是幅度的问题,因为1.5V/500khz又没问题,说明输出达到1.5V是没问题的,那到底是哪里的问题呢?

答案自然是前面提到的压摆率SR的问题了。

压摆率SR

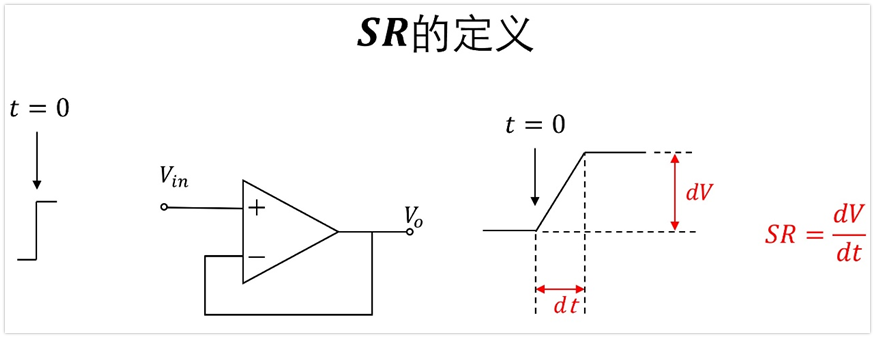

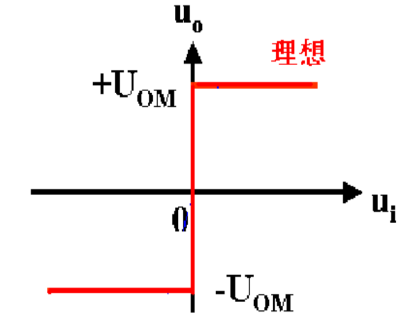

先看下压摆率SR是怎么定义的

运放的压摆率SR 被定义为由输入端的阶跃变化所引起的输出电压的变化速率。它的单位是V/us。

压摆率SR表明了运放输出端所能提供的最大变化速率,如果输出端要想输出比这个速率还快的变化,那么运放就提供不了,这就会导致输出波形变形,原本的正弦波就变成了三角波。

设计中该如何考虑?

简单来说,在设计中,我们一般是知道我们输入的信号是长什么样子的,也知道运放的放大倍数,那么也就知道我们输出信号长什么样子,我们需要保证输出信号的最大斜率小于运放的SR参数就可以了。

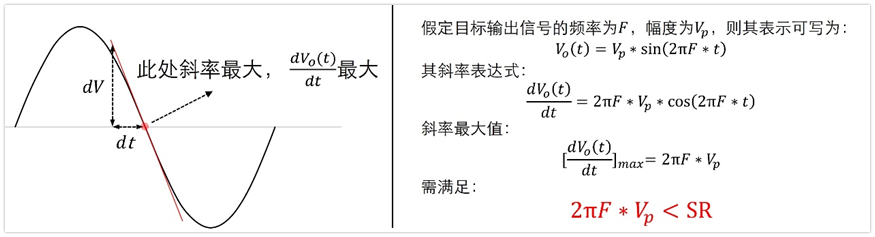

以正弦波为例,假如我们需要运放输出幅度Vp,频率F的信号,那么需要运放的SR达到多大呢?

对于正弦波而言,幅度Vp,频率F信号可以用式子Vo(t)=Vp*sin(2πF*t)来表示。我们可以求得它的斜率表达式(其实就是高中的函数求导):

dVo(t)/dt=2πF*Vp*cos(2πF*t)。

我们很容易求得这个dVo(t)/dt的最大值为:2πF*Vp,也就是说我们需要这个值小于运放的SR。

即:2πF*Vp

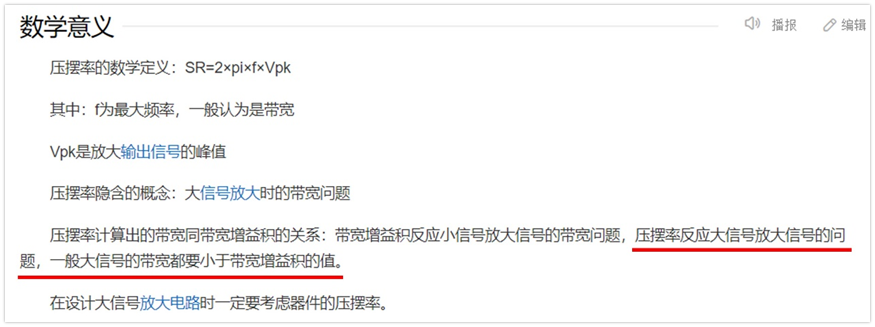

式子2πF*Vp里面有两个变量,一个是信号幅度Vp,一个是信号频率,在信号幅度比较小,频率低时,2πF*Vp满足。与此同时,频率一般会受到带宽的限制,所以,输出信号幅度小的时候,频率满足增益带宽积要求时,压摆率一般不会有问题。而信号幅度大的时候,即使频率在增益带宽积范围内,也有可能因为压摆率不够导致信号失真。

关于上面这一点,百度百科说得很清楚:

回到前面的问题

前面的例子中,我们有三种输入的情况,对应期望的输出信号是

a、1V/1Mhz

b、1.5V/1Mhz

c、1.5V/500Khz

我们使用公式:[dVo(t)/dt]max=2πF*Vp分别计算下这三个信号的最大斜率为:

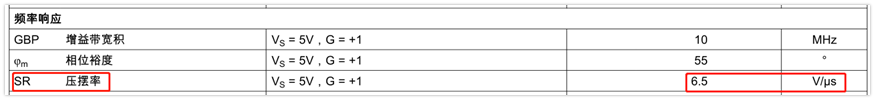

a、1V/1Mhz时最大斜率:2*3.14*1000000Hz*1V=6280000V/s=6.28V/us

b、1.5V/1Mhz时最大斜率:2*3.14*1000000Hz*1.5V=9.42V/us

c、1.5V/500Khz时最大斜率:2*3.14*500000Hz*1.5V=4.71V/us

我们再从运放TLV9061手册中得到其压摆率SR=6.5V/us

可以看到,a和c两种情况都是满足最大斜率[dVo(t)/dt]max运放的能力输出不了9.42V/us这么快,所以输出就失真了。

以上就是为什么我们输入1.5V/1Mhz正弦波,输出波形严重失真的原因。

小结

本期就写到这里了,主要讲了啥是压摆率SR,并且设计过程中可以用公式:2πF*Vp来评估运放的SR是否满足要求。

不过需要注意,这里的信号指的是正弦波,如果非正弦波信号输入,可以直接评估其上升沿dV/dt,如果不成立,则信号的边沿会被运放强行变缓为SR(可以从SR定义里面看出,输入阶跃信号,输出信号的边沿以SR的斜率化)。

仿真源文件下载

在我的微信公众号“硬件工程师炼成之路”后台回复“炼成之路”,就可以下载了,放置在了:器件—>运放—>仿真文件文件夹里面了(注意:需要把spice文件tlv9062.lib放置到自己电脑的库路径下面)。

关于压摆率SR的内容,TI也有对应的视频教程,可以去看看,链接如下:

https://edu.21ic.com/lesson/1911

扫码关注

扫码关注

![电子设计:云源软件安装及程序下载[零基础学FPGA设计-理解硬件编程思想]](https://api.fanyedu.com/uploads/image/56/f26c7093f8fcbe3907793cac815396.png)

![电子设计:数字信号处理课程小结(已完结)[学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/7b/4fe86c99962d21ce79ff1fea61046d.png)