在高速数字电路设计中,过孔的寄生电感问题是电子工程师经常面对的问题之一,寄生电感的存在很容易影响电路的性能,甚至引发意想不到的问题,因此必须及时计算电感然后解决问题,那么如何计算

首先在计算寄生电感问题之前,必须先了解寄生电感到底是什么?简单来说,寄生电感是指电路中原本没有设计地哪敢,但由于某些原因,如过孔产生的电感效应,过孔的寄生电感会对蒂娜鲁中的电流产生阻碍影响,从而影响到电路的性能。

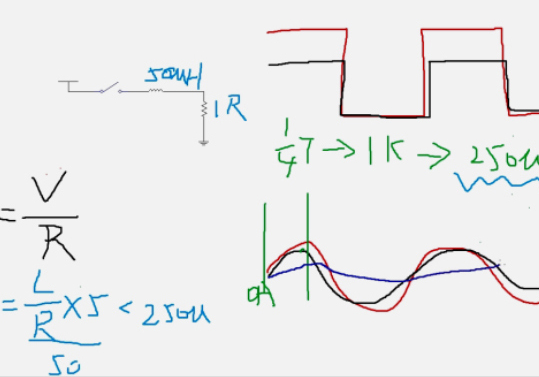

然后,如何计算过孔的寄生电感?

公式:L = 5.08h[ln(4 h/i) +1]

式中L代表过孔的寄生电感,h代表过孔的长度,d代表过孔的中心钻孔直径。

从式中可以看出:过孔的直径对寄生电感的影响较小,而长度才是影响寄生电感的关键因素。所以,在设计电路板时,要尽量减小过孔的长度,以提高电路的性能。

举例,假设:一个过孔的长度为0.05米,中心钻孔直径为0.01米。将这些数据代入公式,我们可以得到:

L = 5.08 × 0.05[ln(4 × 0.05/0.01) + 1] = 1.015纳亨利(nH)。

那么,这个寄生电感对电路有什么影响呢?我们知道,当信号的上升时间是1纳秒时,过孔的等效阻抗大小为XL=T10_90/7(T10_90)=3.19Ω。这个阻抗在高频电流通过时是不能被忽略的。这意味着,如果我们在连接电源层和地层时需要通过两个过孔,那么过孔的寄生电感就会成倍增加。

因此,工程师们在计算过孔寄生电感时需要特别注意以下几点:

首先,要尽量减小过孔的长度;

其次,在连接电源层和地层时要尽量减少过孔的数量;

最后,在设计电路时要充分考虑信号的上升时间和频率,以避免因寄生电感问题而影响电路的性能。

本文凡亿企业培训原创文章,转载请注明来源!

扫码关注

扫码关注