在电路设计中,我们经常会听见“电感饱和”这个词汇,除了电流弯曲失真、烧坏器件折线表象,在物理上“饱和”到底代表着什么?下面凡小亿将聊聊“电感饱和”,希望对小伙伴们有所帮助。

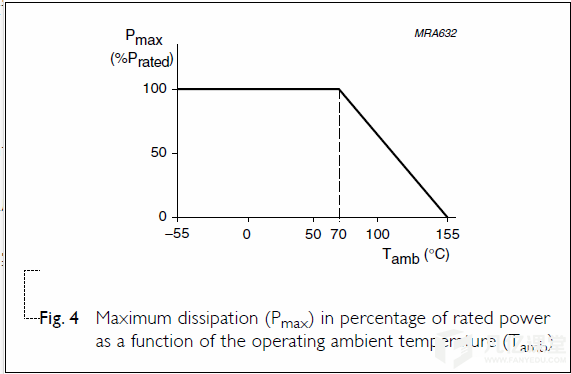

按定义来说,电感饱和是指电感器在电流增大到一定程度后,其感抗不再增加,甚至有所下降现象,这是因为当电流增大时,磁芯的磁通密度增加,但磁芯的磁导率却下降,导致电感的感抗降低。

在电感饱和前,电感的感抗可以表示为:

X = 2πfN^2BS

其中,X为感抗,f为频率,N为线圈匝数,B为磁通密度,S为线圈面积。

然而,当磁芯达到饱和后,磁导率下降,导致感抗降低。此时,电感的感抗可以表示为:

X = 2πfN^2S(Br/μ)

其中,Br为剩磁密度,μ为磁导率。

由于在电感饱和后,磁导率下降,导致感抗降低,因此电感饱和对电路的性能会产生负面影响。此外,当电流增大时,线圈的发热也会增加,可能导致线圈烧毁或短路。

为了避免电感饱和的发生,电子工程师可采取以下措施来避免:

1、选择合适的磁芯材料

不同的磁芯材料有不同的磁导率和饱和磁通密度,选择高磁导率、高饱和磁通密度的磁芯材料,可增加电感的输出及线性范围;

2、增加线圈匝数

增加线圈匝数可提高电感的感抗,从而增加电感的输出及线性范围;

3、减小电流

减小电流可以避免磁芯饱和的发生,在电路设计中可根据项目需求及实际情况来选择合适的电流值;

4、采用磁屏蔽结构

采用磁屏蔽结构可减小外部磁场对电感的影响,从而增加电感的稳定性和线性范围。

本文凡亿教育原创文章,转载请注明来源!

扫码关注

扫码关注