FPGA图像处理之行缓存(linebuffer)的设计二

作者:OpenS_Lee

01

背景知识

在FPGA数字图像处理中,行缓存的使用非常频繁,例如我们需要图像矩阵操作的时候就需要进行缓存,例如图像的均值滤波,中值滤波,高斯滤波以及sobel边缘查找等都需要行缓存设计。这里的重要性就不在赘述。

02

FPGA实现

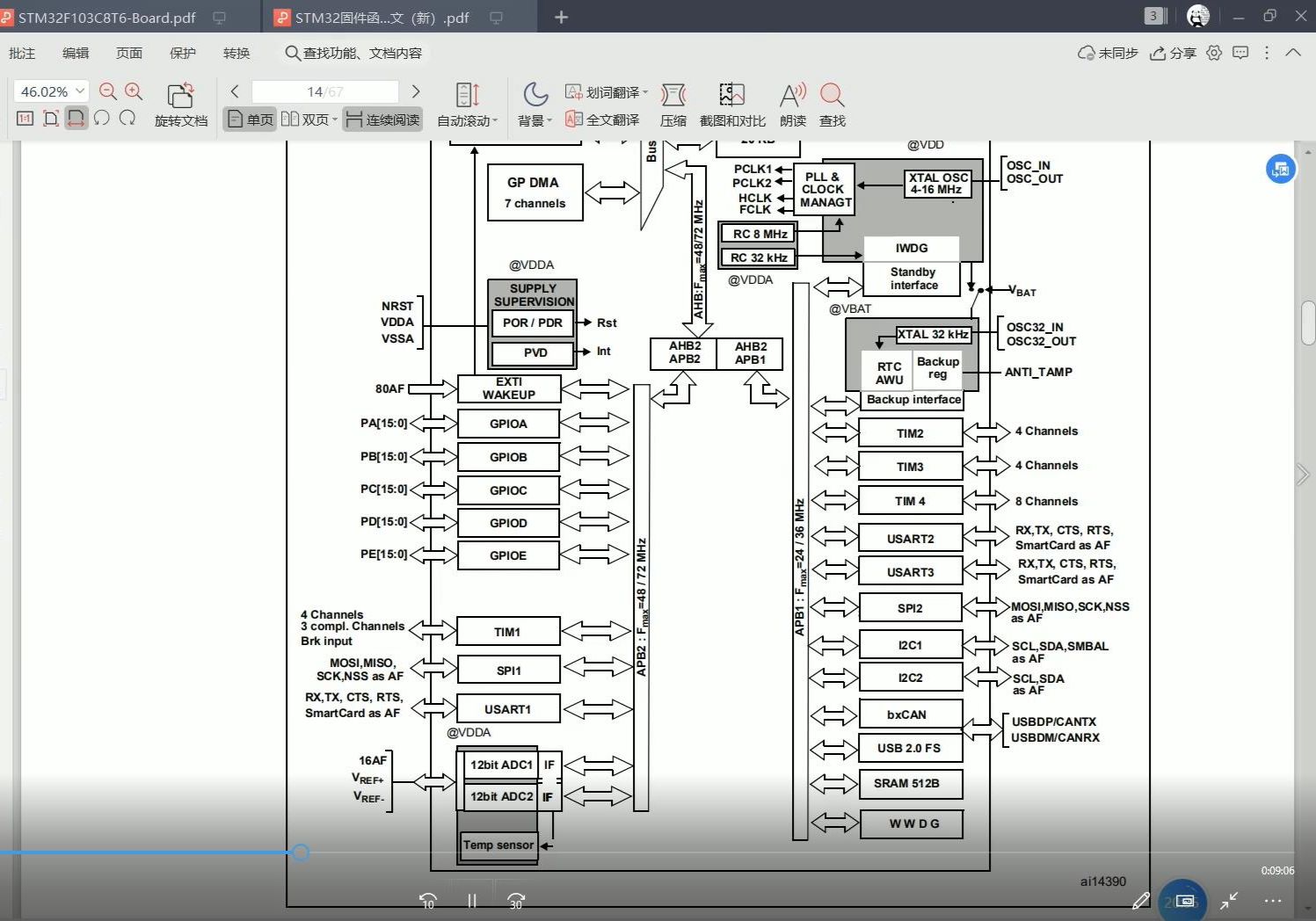

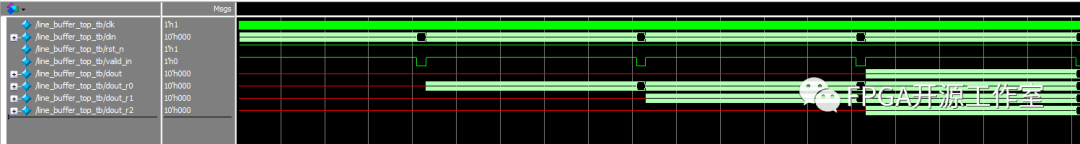

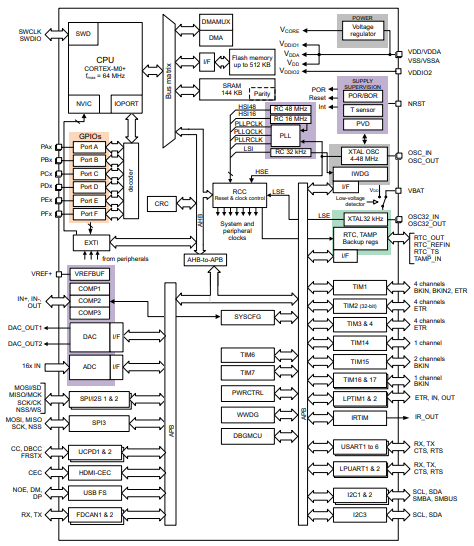

图1 行缓存菊花链结构

如图1所示,我们要设计n行同时输出,就串联n行。Line_buffer的大小设置由图像显示行的大小(图像宽度)决定。例如480*272 (480)。下面我们将采用更加灵活的方法来设计行缓存(linebuffer),使用fifo来设计。

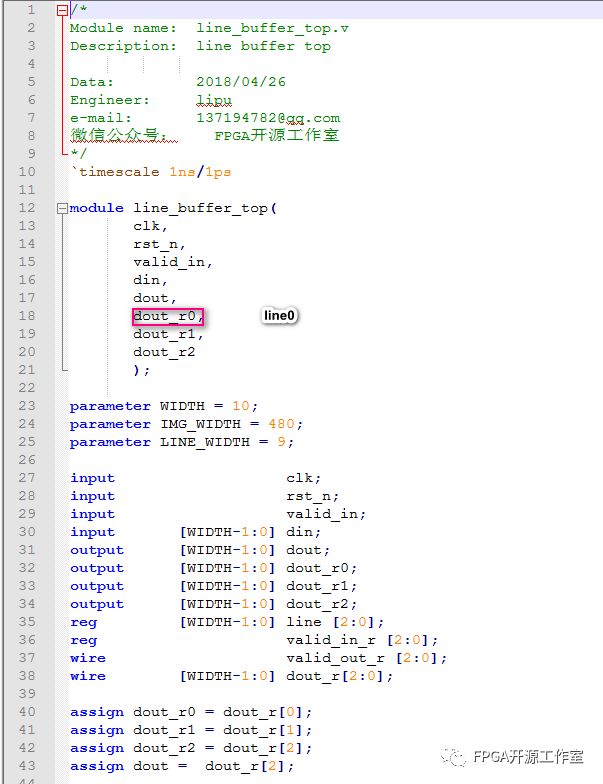

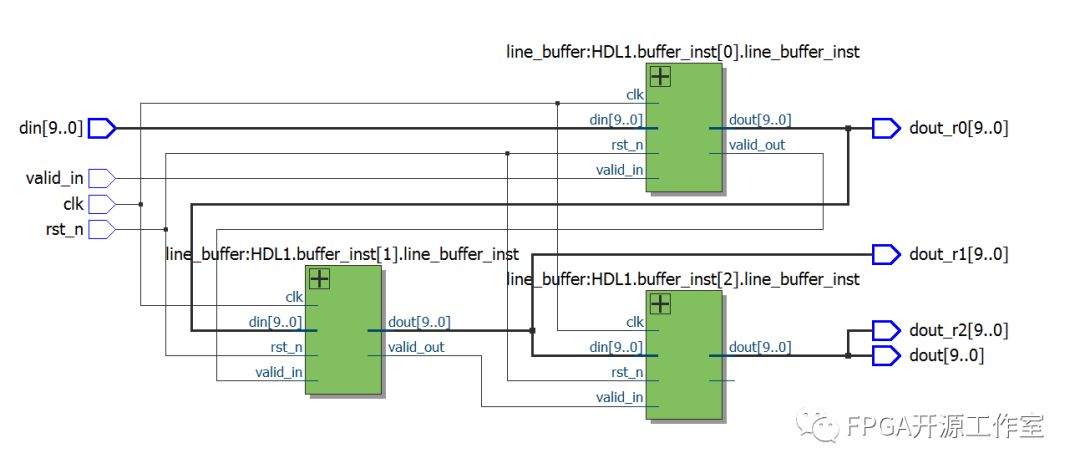

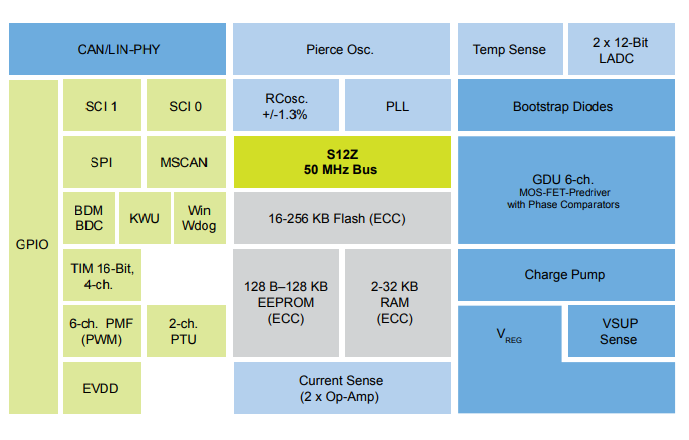

图2 Hierarchy

如图2所示,我们设计了3行行缓存,总共使用了三个fifo。

FPGA源码

1 line_buffer_top模块

如果我们需要缓存5行,7行或更多只需要增加i。这样使得我们的设计更加容易移植和维护。

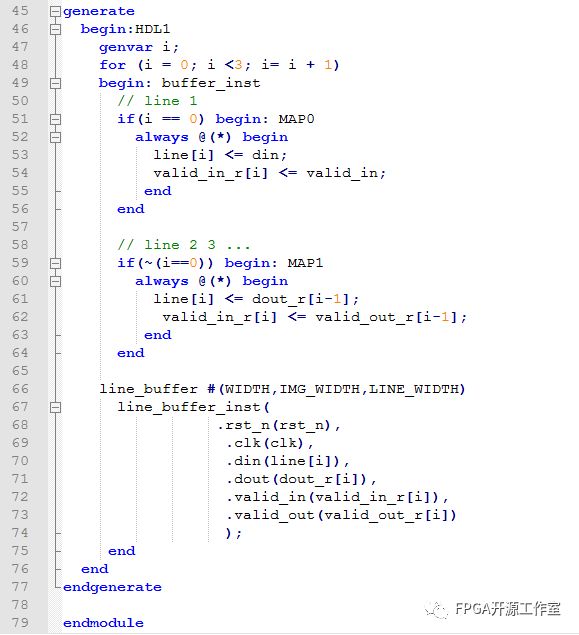

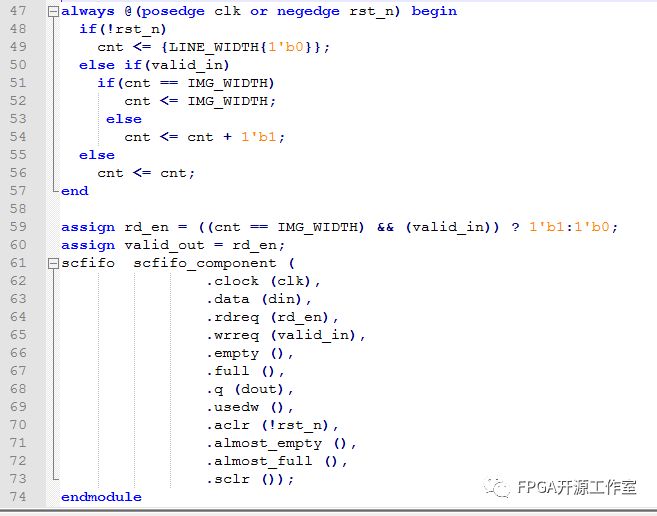

2 line_buffer 模块

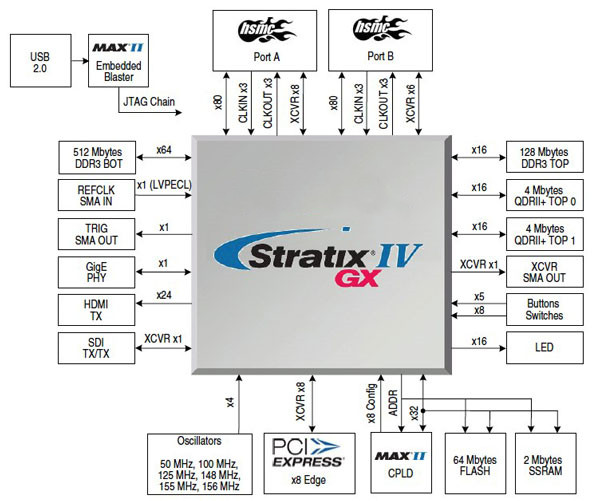

如果需要移植到其他FPGA芯片我们只需要将FIFO替换,或者修改scfifo_component.intended_device_family = "Cyclone IV E"为相应的器件。

RTL viewer

图3 RTL图

如图3所示,整个linebuffer由3个line_buffer组成,最终输出3行缓存数据。

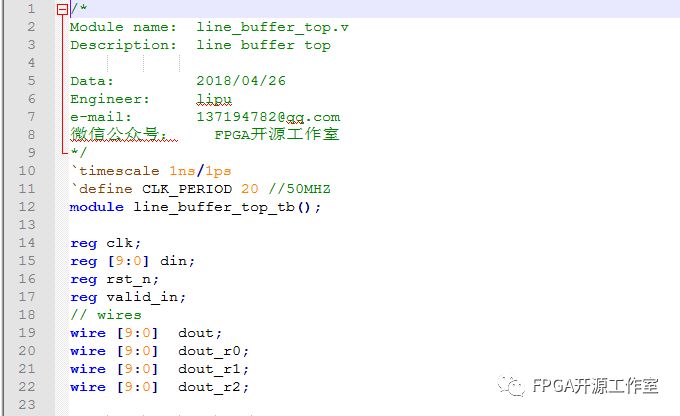

仿真顶层:

仿真结果

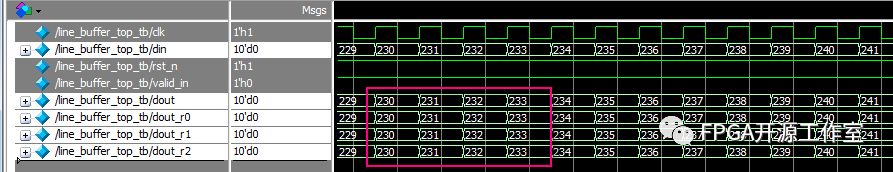

图4 整体仿真效果

图5 数据对齐输出

设计成功。

扫码关注

扫码关注

![电子设计:如何才算学会了FPGA?[零基础学FPGA设计-理解硬件编程思想]](https://api.fanyedu.com/uploads/image/66/620776fd2b3ad7be7fe4984c6c80a5.png)