虽然在芯片工艺上,台积电和三星有所分歧,台积电为保证良品率优势,依然坚持在3nm制程采用FinFET工艺,而三星相比台积电品牌号召力不足,为抢先优势,毅然在3nm制程采用GAAFET技术。

虽然在芯片工艺阶段,台积电比三星晚采用GAAFET,但目前可知的是,根据台积电芯片路线规划图,台积电将在2nm工艺制程采用GAAFET技术。

近日,据供应链厂商透露,台积电将在2025年如期上限2nm生产工艺,并在2025年下半年进入量产阶段,据了解量产地点是中国台湾新竹市宝山乡。

同时台积电计划将在2026年推出N2P工艺,相比其他2nm工艺,该工艺的优势是采用背面供电网络(BSPDN)技术。

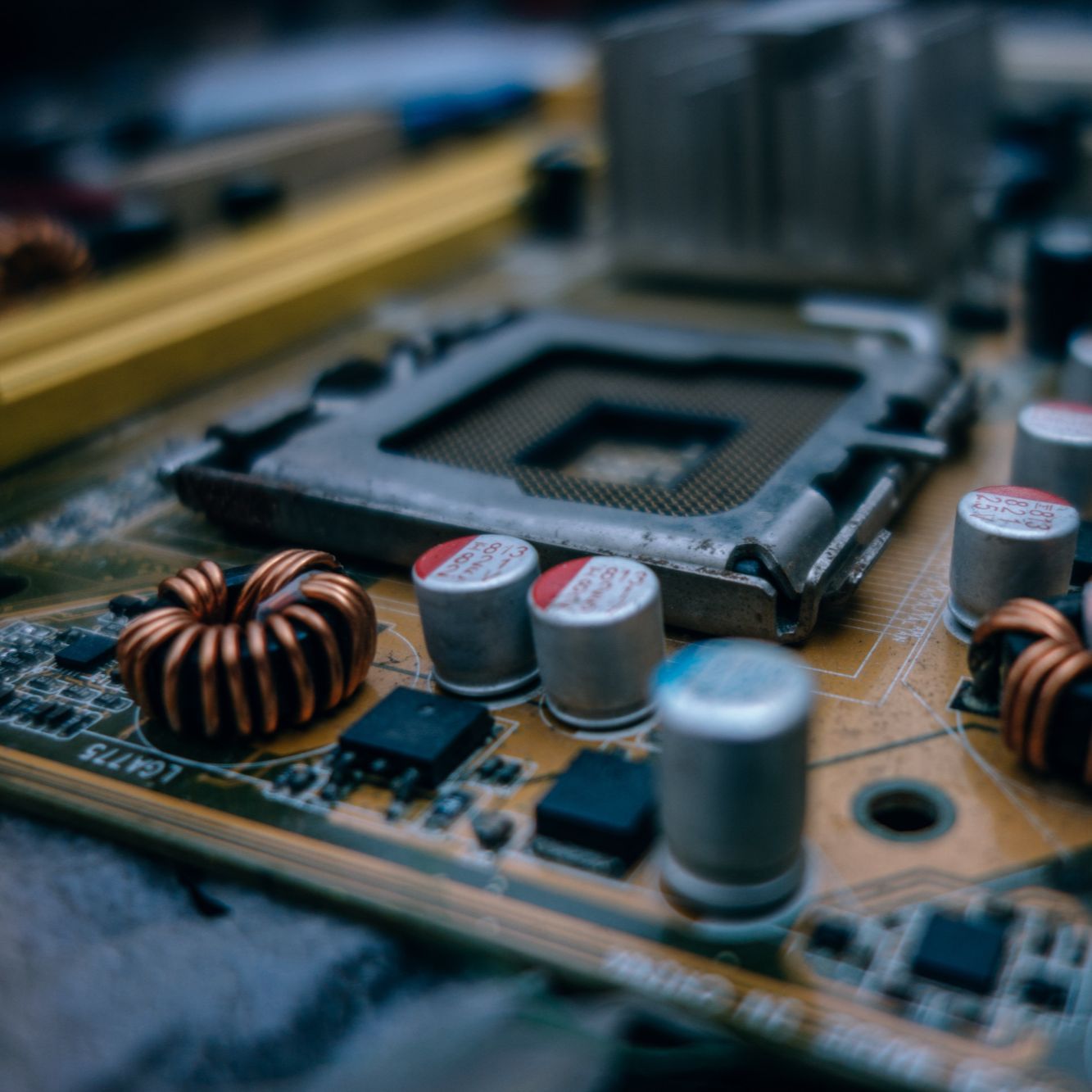

据悉,2nm芯片可以算的上是接近摩尔定律的物理极限,也是台积电在5nm制程工艺的一个重大节点,根据以往爆料,台积电将在2nm制程采用纳米片经过(Nanosheet),即替代鳍式场效应晶体管(FinFET),这意味着台积电将从FinFET正式进入GAA晶体管时代。

在能效方面,相比3nm芯片,2nm芯片在相同功耗下,运行速度将快10-15%;在相同速度下,自身功耗将降低25-30%。而在此过程中,代工技术将从高K金属栅极平面FET发展到FinFET再到MBCFET,最后到BSPDN,除此之外三星也宣布将在2nm工艺采用BSPDN技术。

扫码关注

扫码关注