若工程师在进行高频电路时,如果没处理好电源/地平面的问题,很容易爆发SSN问题,耽误项目进度,所以很多工程师在设计前都会尽量减少SSN问题,下面就介绍减少芯片的SSN方法,希望对小伙伴们有所帮助。

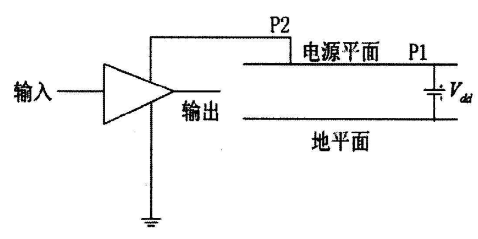

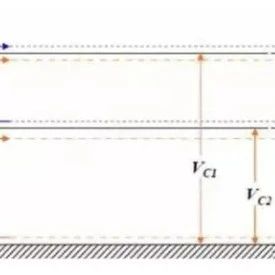

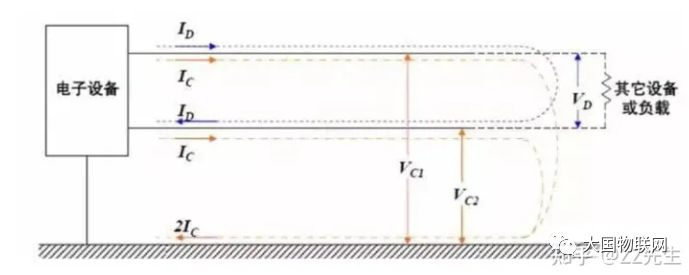

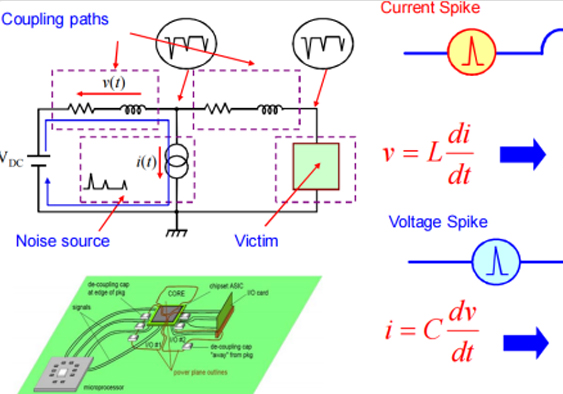

一般来说,在高频电路时,由于寄生效应的存在,电源/地平面可等效为复杂的RLC网络,因此当PCB板上的动态驱动器快速切换时,很容易产生瞬间电流,导致电源平面电压波动,而这种电压噪声被叫做SSN,并且,随着同时切换状态的驱动器数目的增加噪声电压会越来越大,噪声叠加到电源电压上会造成逻辑电路的误判,影响电子元件正常工作。

而减少芯片外SSN的常见措施如下:

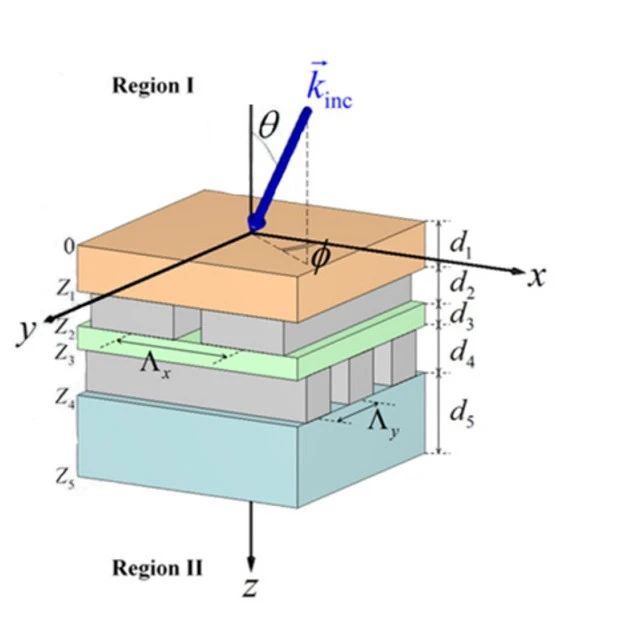

1、尽量使用高阻抗表面设计,以此抑制SSN沿电源平面的传播;

2、不完整的地平面会导致信号变差,所以PCB设计应尽量保证地平面的完整性;

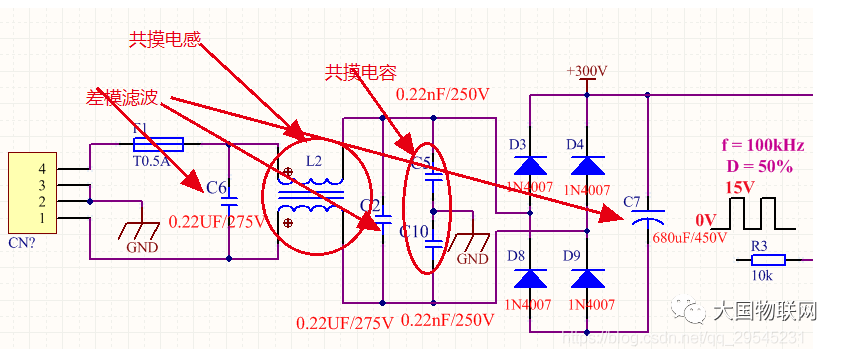

3、可在某些敏感元件引脚附件添加去耦电容,以此降低SSN对元器件的影响;

4、若进行PCB封装,应尽量降低封装回路的电感,或增加信号线与电源/地平面的耦合电感;

5、在PCB设计时尽量不使用过孔,同时对过孔位置和大小进行优化设计,综合考虑过孔的布局;

6、若决定在PCB多层板中采用电源/地平面,将元件的电源和地引脚尽量焊接在电源和地平面上,以减小寄生电感和阻抗;

7、若要减小回路电流的等效电感,工程师可在封装内不使用旁路电容,从而使电源和地共同分担电流回路,使噪声流入地面。

扫码关注

扫码关注

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第三部]](https://api.fanyedu.com/public/uploads/image/course/20200519/55b5b9f147397aa1097829400b322791.jpg)

![电子设计:工程中的带通采样定理 [学以致用系列课程之数字信号处理]](https://api.fanyedu.com/uploads/image/8d/7cf32c2b7d6d9e85bef18595362eea.png)