- 全部

- 默认排序

随着高速电路的不断涌现,PCB板的复杂度也越来越高,为了避免电气因素的干扰,信号层和电源层必须分离,所以就牵涉到多层PCB的设计。在设计多层PCB电路板之前,设计者需要首先根据电路的规模、电路板的尺寸和电磁兼容(EMC)的要求来确定所采用的电路板结构,也就是决定采用4层,6层,还是更多层数的电路板。这就是设计多层板一个简单概念。 确定层数之后,再确定内电层的放置位置以及如何在这些层上分布不同的信号。这就是多层PCB层叠结构的选择问题。层叠结构是影响PCB板EMC性能的一个重要因素,一个好的叠层设计方案将会

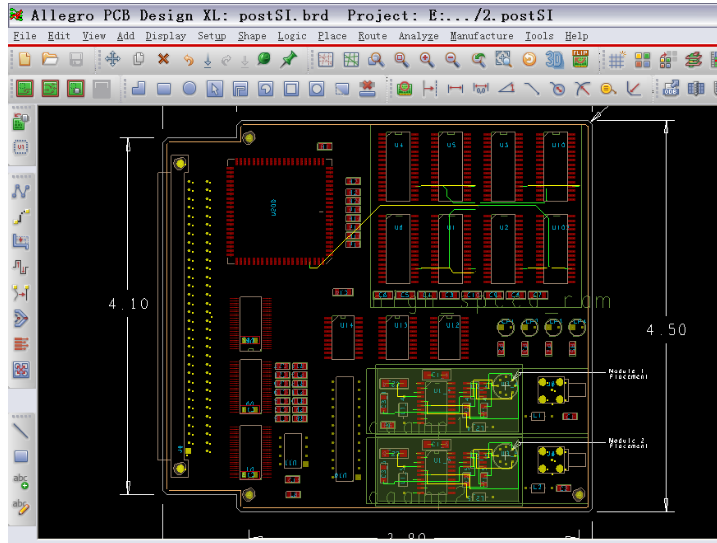

Cadence17.4软件的界面变化后,软件的功能也进行了很大的调整,更加能够适应高速电路和高密度,柔性和刚柔结合设计,背钻异形槽孔的设计等。

Cadence17.4软件的界面变化后,软件的功能也进行了很大的调整,更加能够适应高速电路和高密度,柔性和刚柔结合设计,背钻异形槽孔的设计等。

Cadence17.4软件的界面变化后,软件的功能也进行了很大的调整,更加能够适应高速电路和高密度,柔性和刚柔结合设计,背钻异形槽孔的设计等。

课程基于实例介绍和演示HFSS在天线、微波器件和高速电路中的应用,让读者掌握HFSS在天线仿真、微波器件设计、高速信号仿真等方面的应用

在高速电路设计中,链路中的每一个参数都有可能导致传递的信号出问题。今天就和大家分享一个平常大家不太注意的参数。 先回顾下在中学的时候,咱们学习的一个概念,趋肤效应:当信号的频率较越来越高时,信号都会趋向于导体的表面传递。这样就会导致信号流过导体的相对有效面积变小,从电阻的角度来分析,这就会导致电阻增加,导致传递能量的损失。 在电子产品使用的PCB,基本都是由铜箔和有机材料组成的 我们平时看到的铜箔,表面上看起来都是非常光滑的,实际上并不如你肉眼所见的那样,铜箔并不是完全光滑的。

设计高速电路板的注意事项 怎样引起实际阻抗发生变化的,以及怎样用精确的现场解决工具(field solver)来预见这种现象。即使没有工艺的变化,其它因素也会引起实际阻抗很大的不同。在设计高速电路板时,自动化设计工具有时不能发现这种不很明显但却非常重要的问题。然而,只要在电路设计的早期步骤当中采取一些措施就可以避免这种问题。我把这种技术称做“防卫设计”(defensive design)。

在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错。那么如何区分高速信号和普通信号呢?很多人觉得信号频率高的就是高速信号,实则不然。我们知道任何信号都可以由正弦信号的N次谐波来表示,而信号的最高频率或者信号带宽才是衡量信号是否是高速信号的标准。在高速PCB电路设计过程中,经常会遇到信号完整性问题,导致信号传输质量不佳甚至出错

高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。

扫码关注

扫码关注

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第二部]](https://api.fanyedu.com/public/uploads/image/course/20200518/92b8de8dc1073a42c2d24b16c709e55e.jpg)

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第一部]](https://api.fanyedu.com/public/uploads/image/course/20200516/146c7f84154ccbf93c281a00756c6906.jpg)

![Cadence17.4 GD32 ARM高速电路PCB硬件设计实战[第三部]](https://api.fanyedu.com/public/uploads/image/course/20200519/55b5b9f147397aa1097829400b322791.jpg)