- 全部

- 默认排序

嵌入式硬件电路设计基本功

我走的电子开发道路其实和大多数人说的一样,基本的路线为模拟电子(熟练)→数字电路设计(掌握)→单片机(项目开发)→ARM硬件设计(项目开 发)→linux学习→linux驱动学习→ARM&linux底层开发(项目开发)→ARM&linux顶层开发(项目开发)→项目经理。我现在还在路上

如何正确做好数据治理?

在数据智能运用的道路上,数据烟囱、信息孤岛遍布。由于顶层设计的缺失及历史原因,企业的各个业务系统、管理系统等的数据壁垒问题严重。另外,由于所用技术不同、开发团队水平不一、开发平台和工具不统一、缺乏规范的数据管理标准,各个系统间的数据难以兼容

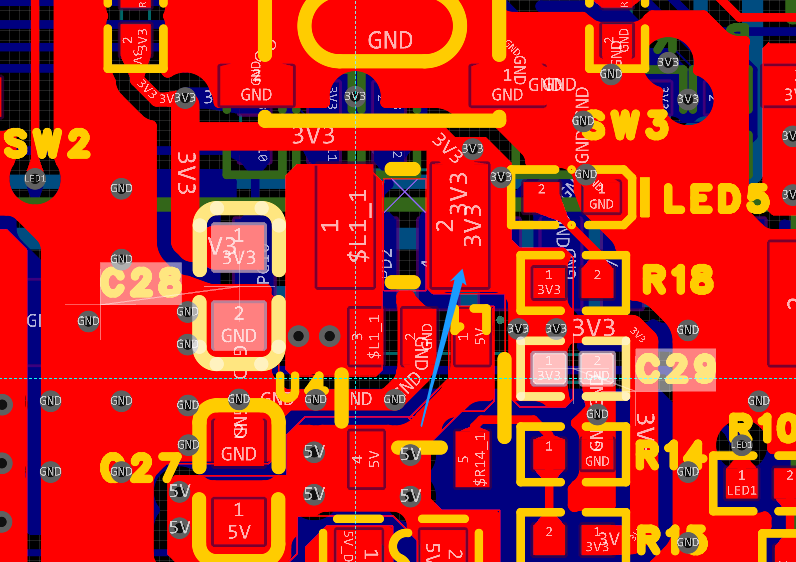

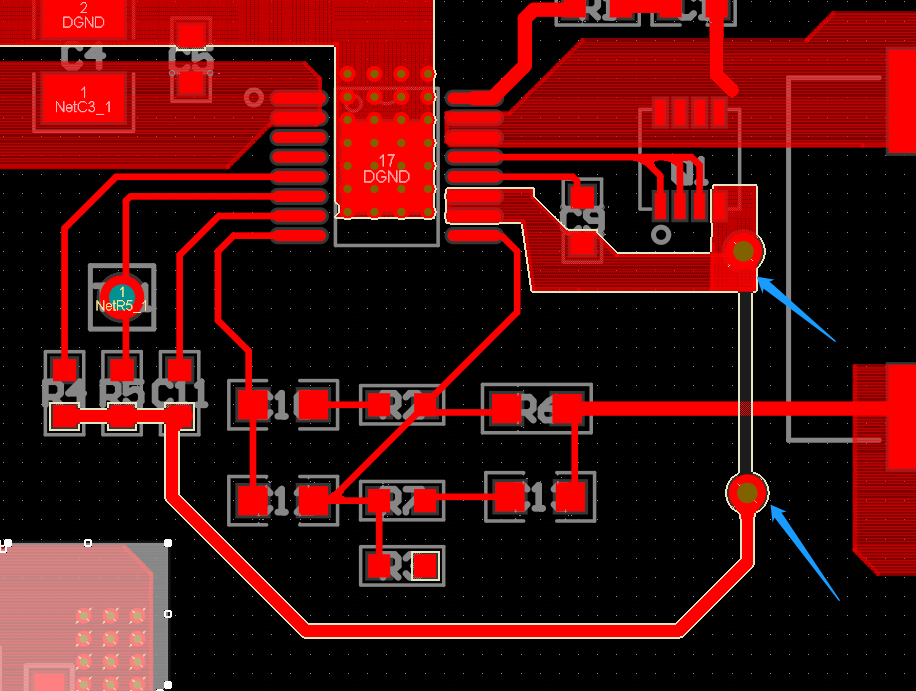

电源输出的滤波电容要靠近输出管脚放置2.USB的电容放置不到位,应该线经过电容在连接到USB器件,差分出线要耦合出线,走在一起3.器件干涉4.SDRAM的滤波电容尽量保证一个管脚一个5.顶底层器件干涉,顶层器件是插件,你底层也放器件,后期不

自从华为和中芯国际等中企受到美国无理的打压,国人开始重视半导体供应链的独立自主,作为半导体顶层产业的核心集成电路设计产业更是被寄托希望,新的一年,中国集成电路设计产业该如何保持优势,应付未来的挑战?若是要解决现状问题和应对未来挑战,首先要正

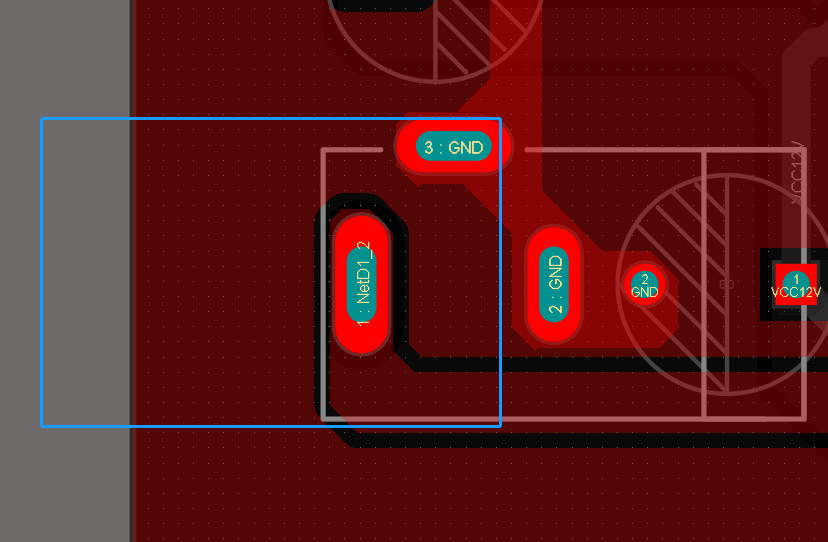

电源座子需要靠近板边放置2.pcb上存在短路3.滤波电容靠近跨接电感放置4.输出主干道尽量铺铜处理5.输出滤波电容先大后小进行摆放6.反馈从最后一个滤波电容后面取样,走一根10mil的线即可7.主干道器件尽量顶层放置8.中间的散热焊盘需要打

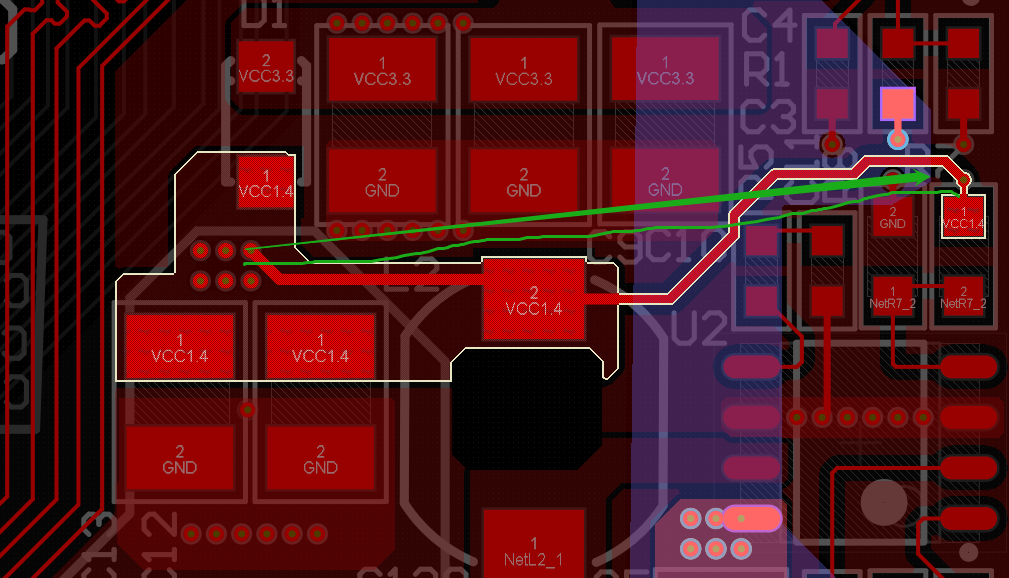

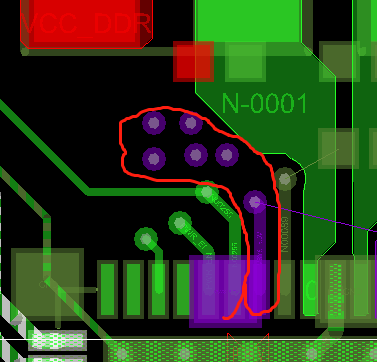

反馈要从电容后面取样2.注意过孔不要上焊盘3.走线尽量不要从电阻电容中间穿4.丝印调整不到位,注意丝印不要上焊盘5.顶层BGA里面的铜尽量挖掉6.此处走5mil地线太细,建议最少12mil以上以上评审报告来源于凡亿教育90天高速PCB特训班

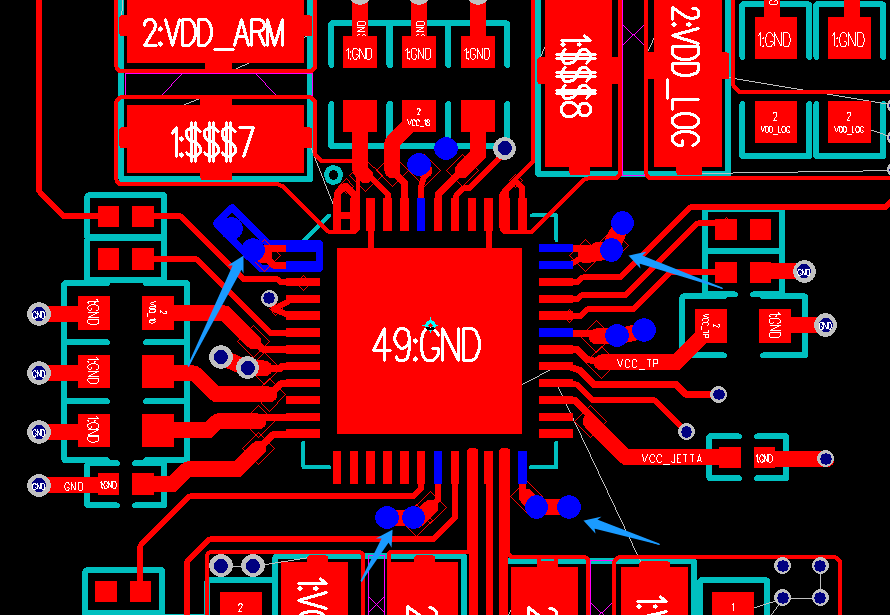

单点接地,此处不用打孔,直接在顶层连通,下面的反馈可以打孔走底层2.反馈要从最后一个电容后面取样3.电容放置应该先大后小4.注意打孔不要离焊盘太近,尽量不要上焊盘5.电感所在层的内部需要挖空处理6.焊盘上存在多余的线头7.存在开路8.散热过

反馈线需要走一根10mil的线,线宽尽量保持一致2.此处是输主干道,两个过孔不满足载流3.存在无网络铜皮和过孔4.此处器件在底层无法与顶层铜皮进行连接5.电源和地存在开路以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB

电源打了几个孔需要再顶层铺铜进行连接,或者走线连接2.电源在底层铺一块铜皮进行连接3.这个电源走一根20mil的线就足够了4.地网络直接打孔在底层铺整版铜,不用进行走线连接5.过孔没有网络6.器件摆放干涉,摆放器件时最好把丝印层打开以上评审

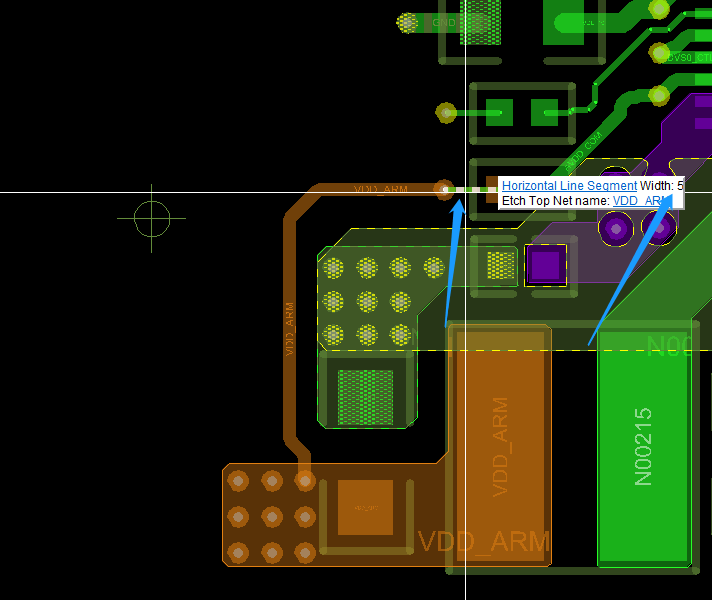

DCDC 4路输入不满足载流,一般20mil过1A2.输出铺铜尽量大一点,地网络尅直接连接在散热焊盘上3.走线需要优化一下4.元件尽量优先顶层布局5.反馈器件尽量靠近管脚放置,走一根10mil的线即可6.反馈需要加粗到10mil7.此处电源

扫码关注

扫码关注