- 全部

- 默认排序

如果您曾经尝试过去除设计的某个区域,您可能会发现这个过程比想象的更加复杂。如果我们使用显示元素(show element)功能来选择该区域中的铺面,就会选中整个形状。这样可能会超出到想要修改的区域之外;区域周边走线也会较为曲折。我们是否要删除整个 cline,再重新连接其他的线?是否会分段删除、减少

由于文章限制,将此文分为上中下三篇,欲看上下文,可点击右侧链接《为什么要遵守这些PCB原则?不做会出大事!(上)》、《为什么要遵守这些PCB原则?不做会出大事!(下)》。原则11:双层板电源走线需紧邻地线平行必要性:确保电源电流回路面积最小

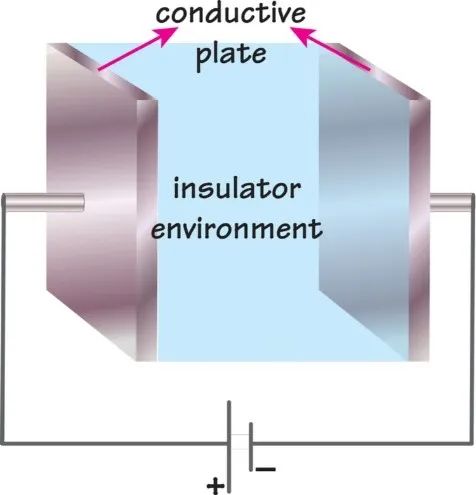

本文要点了解电容性耦合的基本原理。了解电容性耦合的利与弊。了解关于减少电容性耦合的技巧。如果教室里有两个爱说话的小朋友怎么办?当然是让他们的座位离得尽量远一些,这样才能保证课堂秩序和教学效率。这一原则同样适用于 PCB 中的嘈杂走线,本文将探讨电容性耦合的基础知识,并学习如何有效地减少电容性耦合以避

在集成电路(IC)设计即将流片的关键阶段,走线布局成为决定芯片性能、功耗及可靠性的重要因素,合理的走线策略不仅能优化信号完整性,也能有效减少噪声干扰,确保芯片功能的正确实现。1、控制连线长度与增强驱动金属连线应尽量短以减少延迟和信号衰减;长

在通信系统设计中,差分电路因其高线性度和抗共模干扰性能而备受青睐。然而,差分滤波器的布线却是一项复杂而精细的任务,直接关系到系统的整体性能。以下列出差分滤波器布线时需要注意的具体点。1、成对差分走线长度相同确保正负信号走线长度完全一致,以保

大家都知道,要想电路板的散热能力强,除了走线及布局,也要确保电子元器件的散热特点,毕竟良好的散热能力可以增长电子元器件的工作稳定性和寿命。那么如何选择散热能力好的电子元器件?1、器件封装选择查阅器件封装说明,关注热传导率。确保基板与器件封装

在通信系统中,相比单端电路,许多工程师会更加乐意差分电路,因为差分电路有更高的线性度、抗共模干扰信号性能等,当然差分电路并非没有缺点,所以可以通过改善差分滤波器来降低其缺点影响。1、成对差分走线的长度须相同2、差分对内的走线布线须彼此靠近3

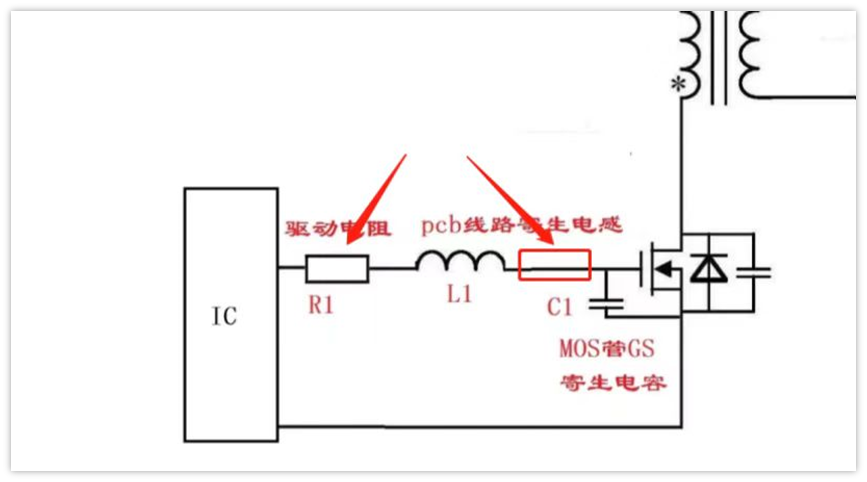

前一段时间有个兄弟问了个问题,把我问住了,问题是这个:如上图,串联的电阻R1到底是放在靠近IC端,还是靠近MOS端?(注意,图中的L1是走线寄生电感,并不是这里放了个电感器件) 我们具体沟通的情况是这样的: 这位兄弟说大部分工程师和IC原厂都是这么做的,但是没有说为什么,我当时也不清楚。但是这个问题

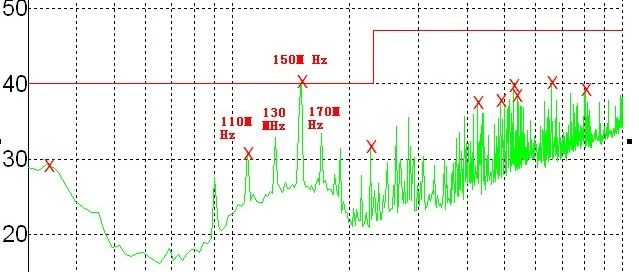

某产品EMC辐射骚扰测试超标,通过近远场扫描配合定位分析,逐步找出骚扰源、传播路径,最终通过修改 PCB 走线切断传播路径解决此问题。1 故障现象 某产品在进行 EMC 研发摸底测试时发现,整机辐射骚扰垂直方向测试超标,超标点频率为 150M Hz,同时伴有 20M Hz 间隔的脉冲骚扰。

在PCB DFM设计中,我们经常会碰见锐角,这个锐角并非我们常说的走线锐角,而是铜元件(如走线)上形成的尖锐或异常角度,这些角度通常在PCB的创建过程中会导致蚀刻酸液的聚集,严重影响PCB的生产效率及产品质量,所以需要解决!1、锐角危害有多

扫码关注

扫码关注