- 全部

- 默认排序

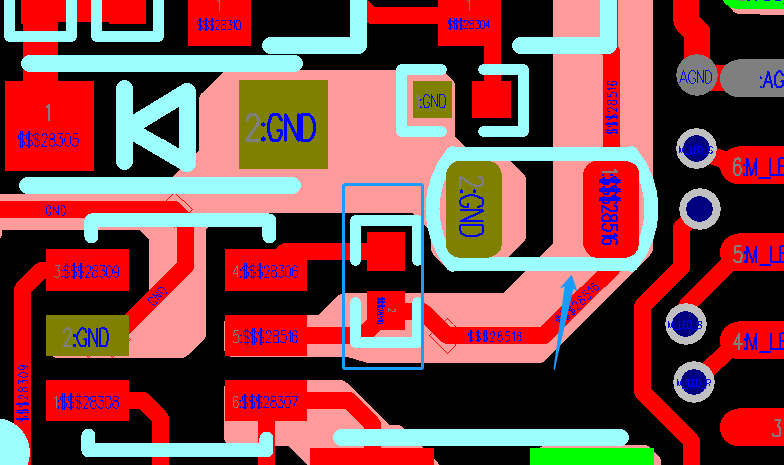

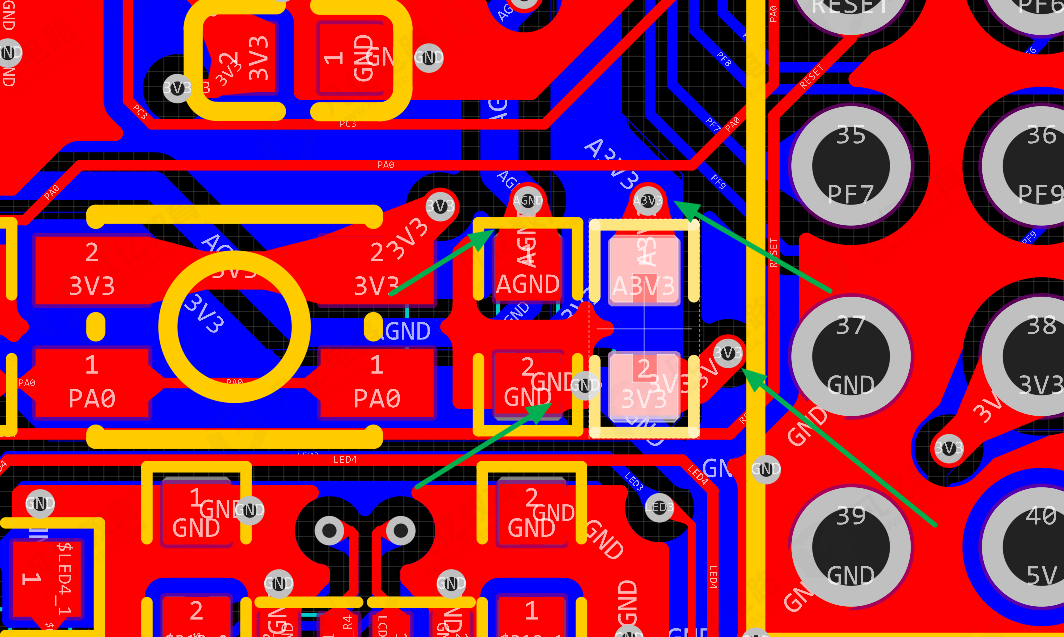

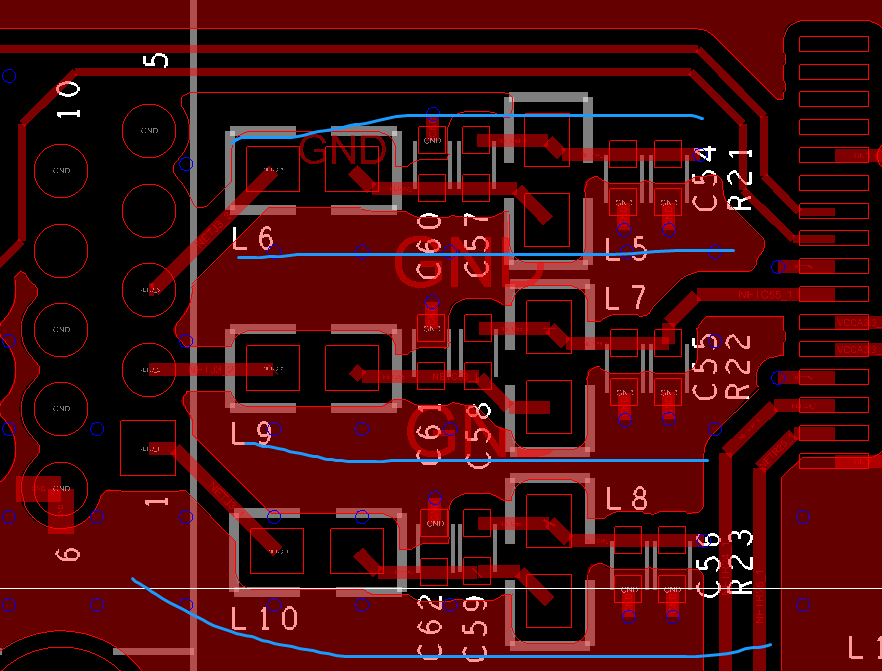

1.布线尽量避免从焊盘宽方向和四角出线,多处出线从宽方向出线。2.需要加粗的走线在焊盘里面需要和焊盘一样宽,出焊盘后再加宽。3.走线避免锐角和线头4.存在很多尖岬铜皮、碎铜、直角锐角铜皮5.继电器和电感容易影响其他信号和污染地网络,器件下方

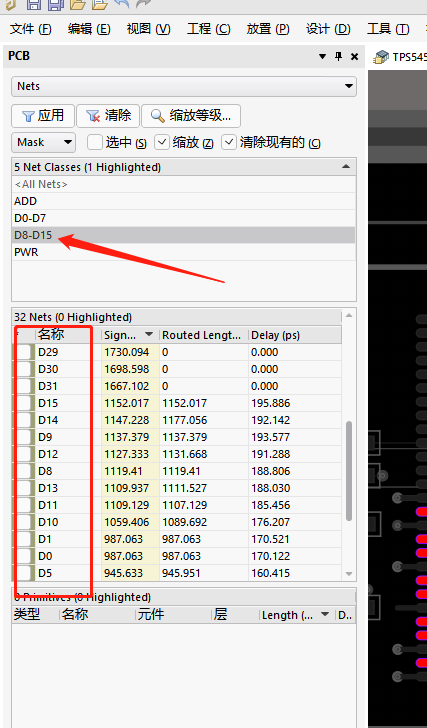

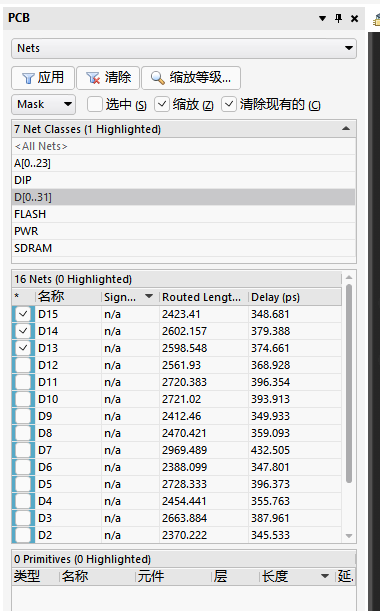

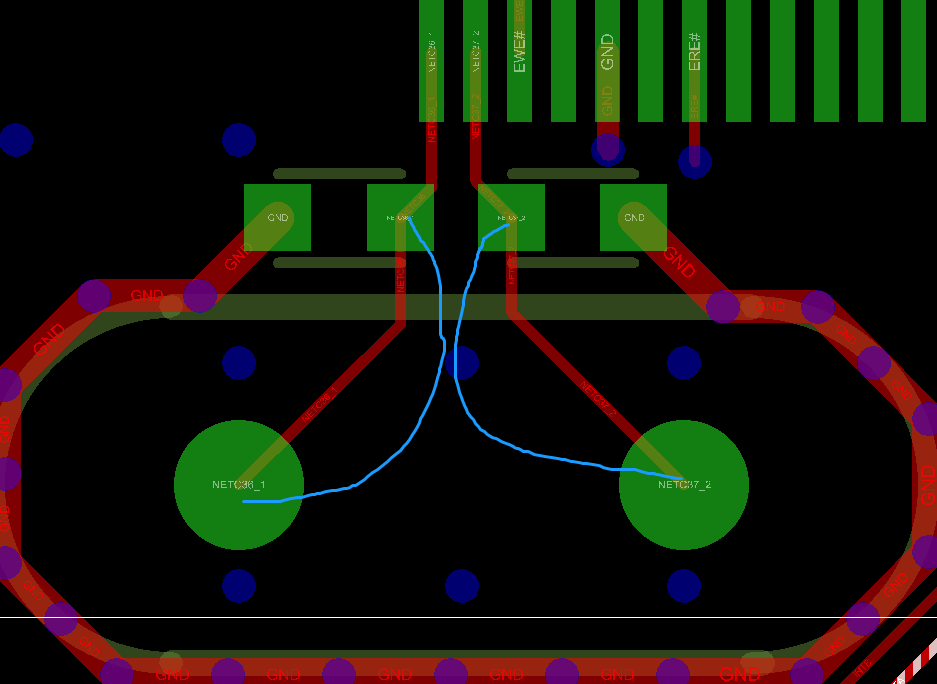

数据线一组只有9根线,其他信号不要添加进来,高八位少一根LDQM12.数据线和地址线建议添加一根最少20mil的地线进行隔开3.过孔里存在多余的线头4.地址线分组错误,有电阻几根网络也需要添加进来进行一起等长,还有时钟信号5.走线需要从焊盘

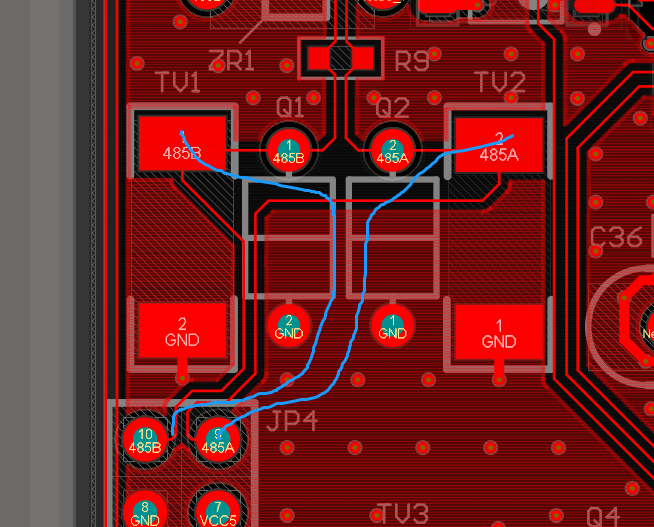

1.485需要走内差分处理2.跨接器件旁边尽量多打地过孔,间距建议2mm3.晶振下面尽量不要走线4.差分走线不满足间距规则以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https

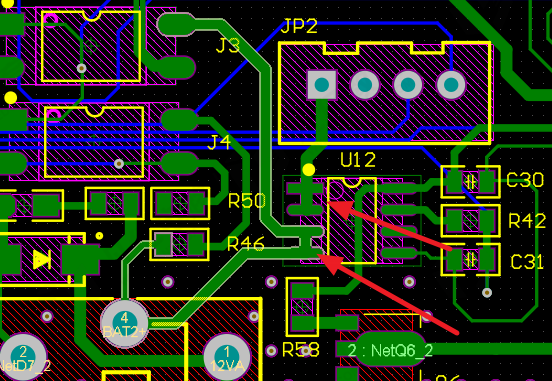

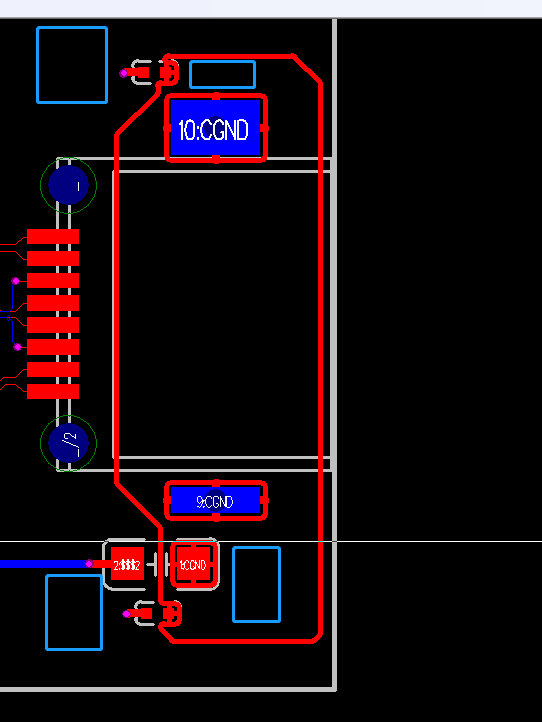

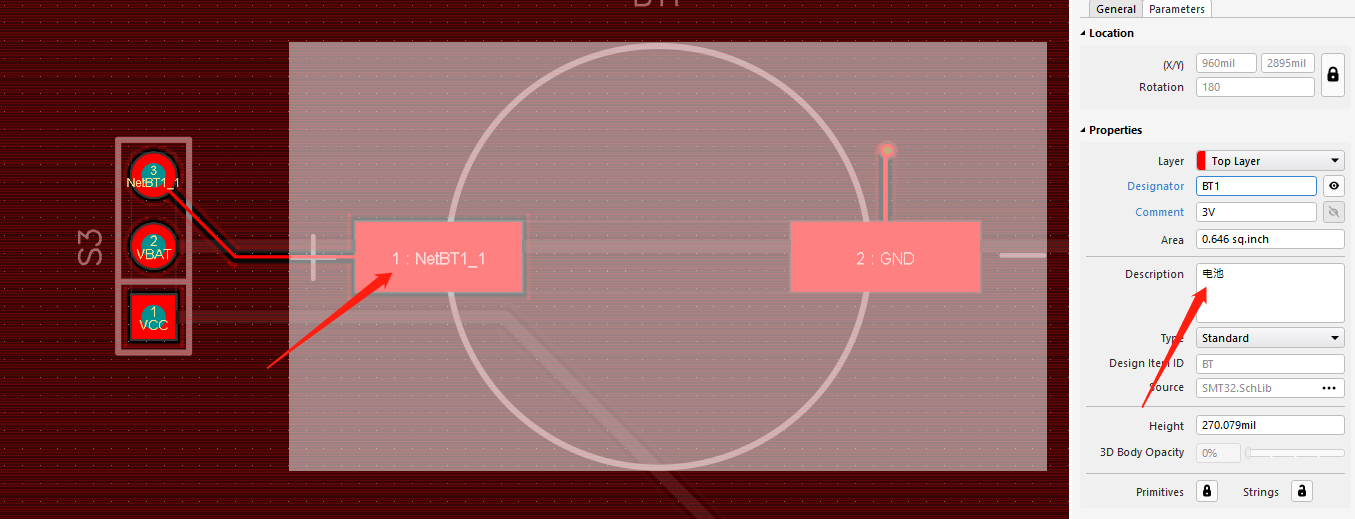

1,输入电容靠近管脚放置2.反馈路劲从最后一个电容后面取样3.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.跨接器件旁边尽量多打地过孔5走线不要有任意角度,尽量从焊盘中心出线6.铺铜和走线选择一种即可7.pcb上存在d

数据线分组错误2.地址线分组错误3.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊4.走菊花链的结构,等长应该是BGA到SDRAM,然后再从SDRAM到FLASH5.相邻焊盘是同网络的,不能直接相连,需要先连接焊盘之后在进

跨接器件旁边尽量多打地过孔2.此处为电源网络,线宽需要加粗3.确认一下此处是否满足载流,线宽尽量一致4.晶振下面不要走线5.差差分之外,其他的信号都需要加粗到20mil6.器件摆放不要挡住1脚标识7.注意等长线之间需要满足3W规则,与时钟信

地缘信号走线需要加粗处理,尽量满足载流2.SD卡需要靠近板框放置3.SD卡信号线需要进行等长处理,误差300mil4.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.晶振需要走内差分,并包地处理,在地线上均匀的打上地过孔

1.模拟数字连接处电容要多打孔加大载流。 2.走线避免锐角,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊3.电源模块输入应该从F1-C31-U4.4pin;要f1连接到c31到u4.4脚在到1脚。4.电源模块输出路径应该铺铜或走线加粗多

模拟信号尽量一字型布局,并单根包地2.锯齿状等长不能超过线距的2倍3.网口除差分信号外,其他都需要加粗到20mil4.电感所在层的内部需要挖空处理5.反馈路劲需要从电容后面取样6.注意数据线直接拿等长需要满足3W规则7.地址线之间也需要满足

晶振走内差分需要再优化一下2.模拟信号走一字型布局,没空间就调整旁边的器件和走线3.跨接器件旁边尽量多打地过孔,间距建议2mm,贴片器件建议离定位孔远一下可以参考一下此图4.地址线,控制线和时钟信号未创建等长组进行等长5.此处走线能拉直尽量

扫码关注

扫码关注