晶振走内差分需要再优化一下

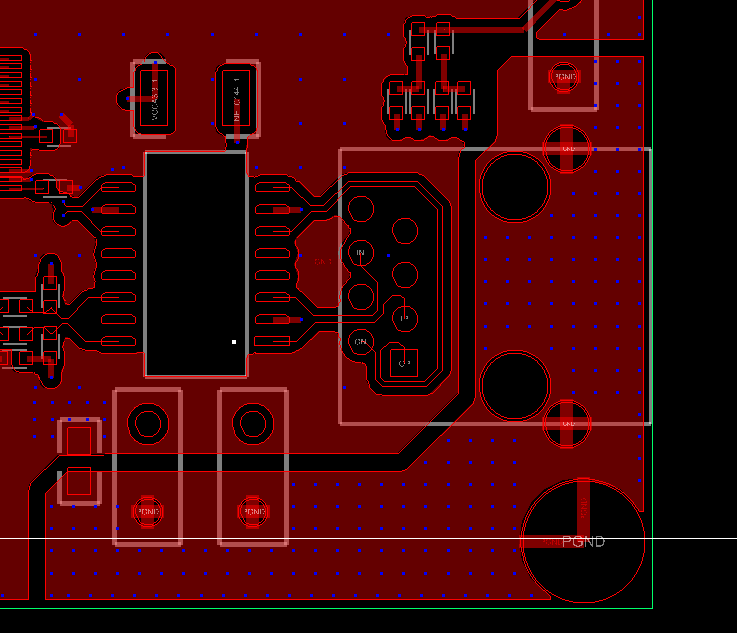

2.模拟信号走一字型布局,没空间就调整旁边的器件和走线

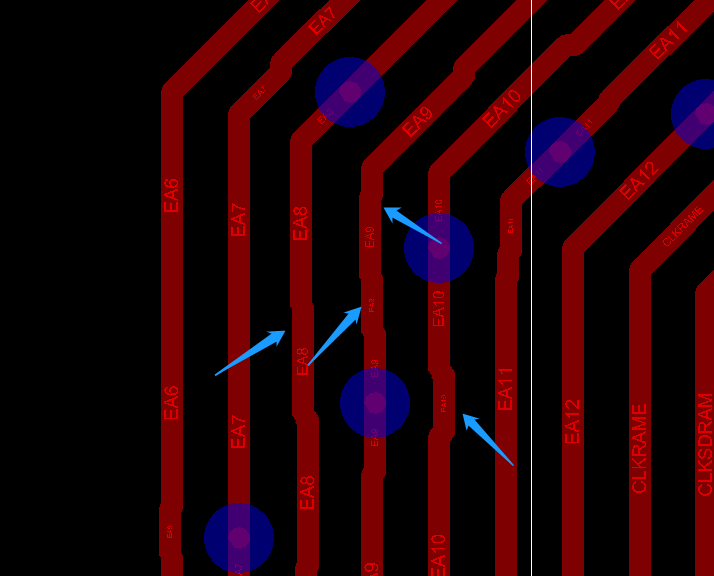

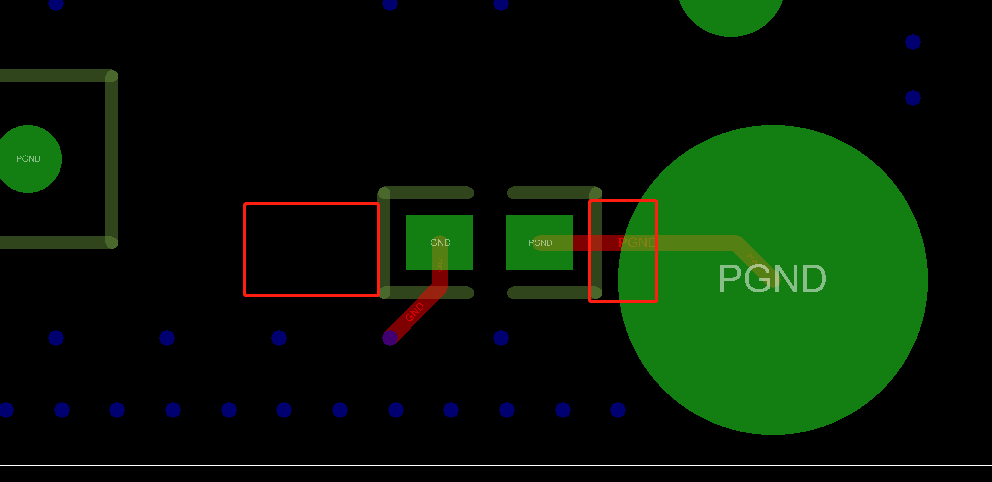

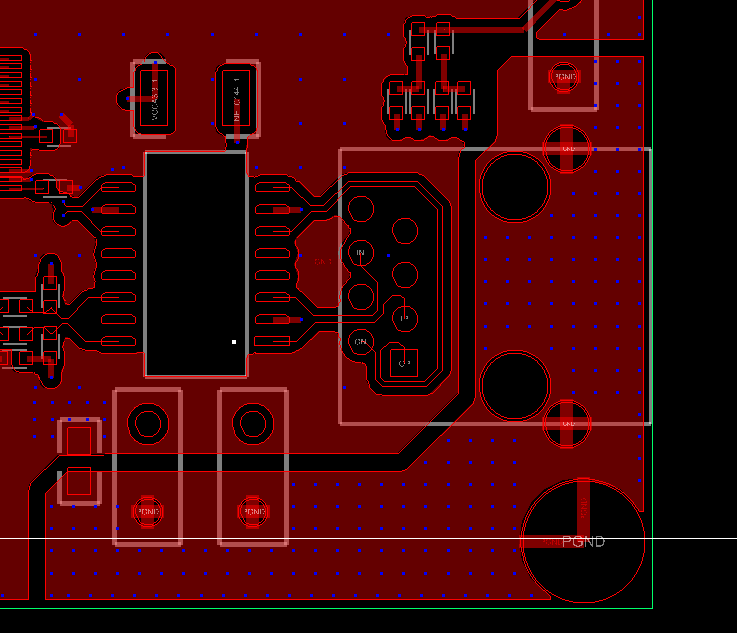

3.跨接器件旁边尽量多打地过孔,间距建议2mm,贴片器件建议离定位孔远一下

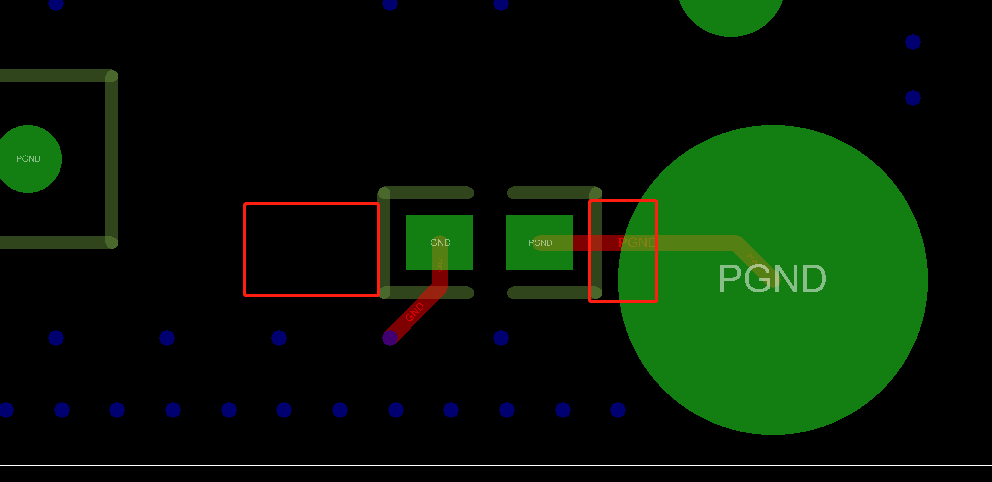

可以参考一下此图

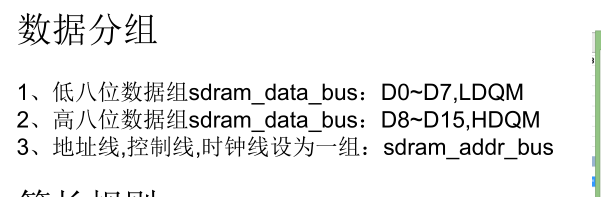

4.地址线,控制线和时钟信号未创建等长组进行等长

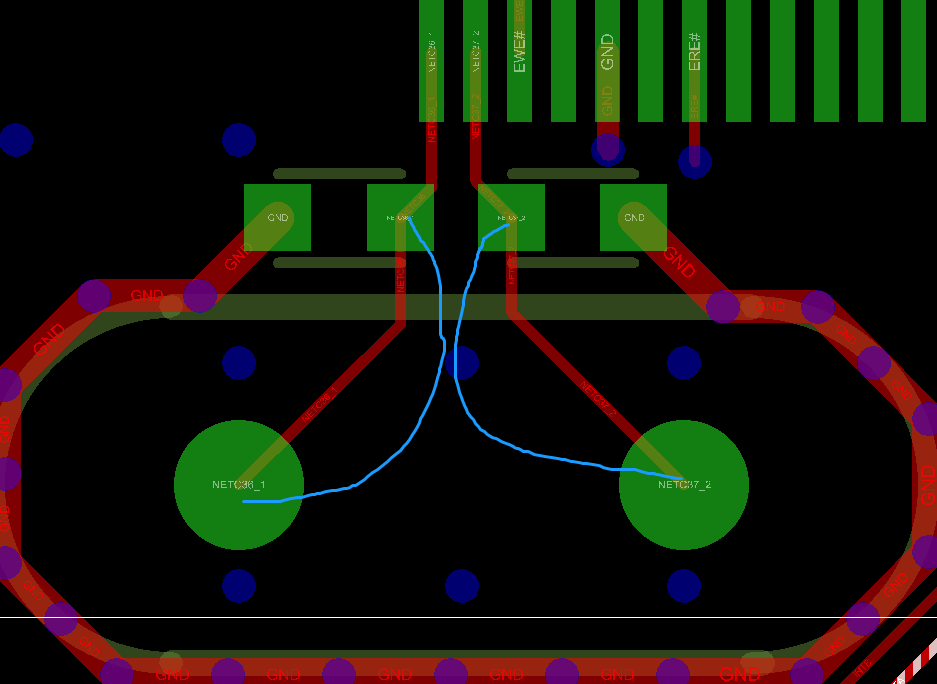

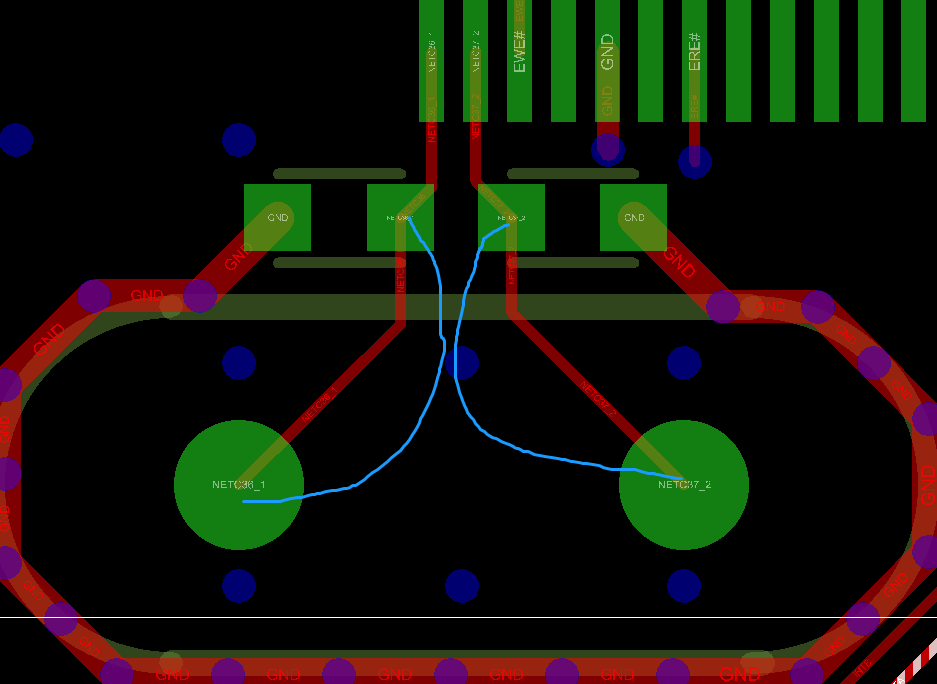

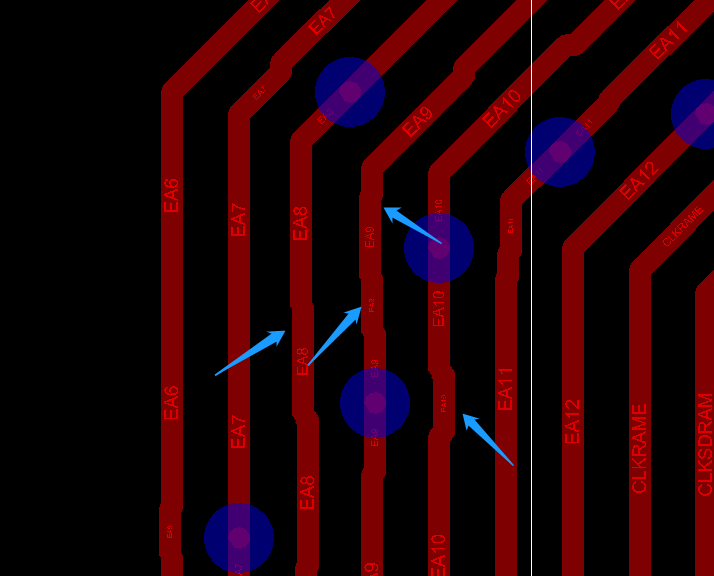

5.此处走线能拉直尽量拉直

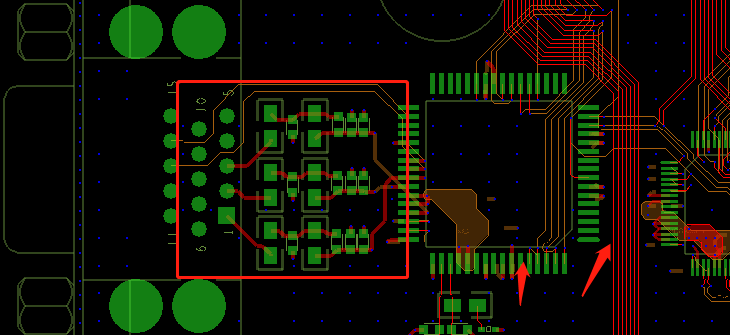

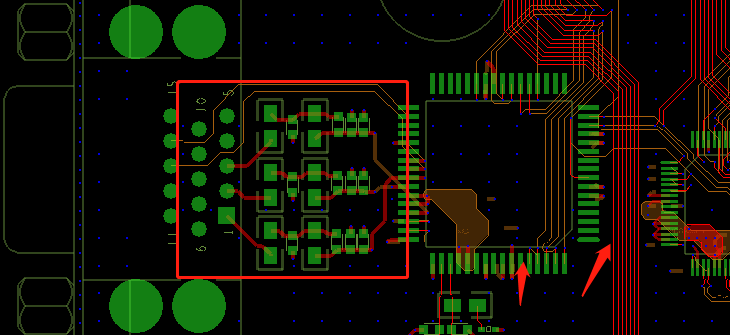

6.这把数据线应该先从BGA到IC在到SDRAM,后期自己优化一下

以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

如需了解PCB特训班课程可以访问链接或扫码联系助教:

晶振走内差分需要再优化一下

2.模拟信号走一字型布局,没空间就调整旁边的器件和走线

3.跨接器件旁边尽量多打地过孔,间距建议2mm,贴片器件建议离定位孔远一下

可以参考一下此图

4.地址线,控制线和时钟信号未创建等长组进行等长

5.此处走线能拉直尽量拉直

6.这把数据线应该先从BGA到IC在到SDRAM,后期自己优化一下

以上评审报告来源于凡亿教育90天高速PCB特训班作业评审

如需了解PCB特训班课程可以访问链接或扫码联系助教: