- 全部

- 默认排序

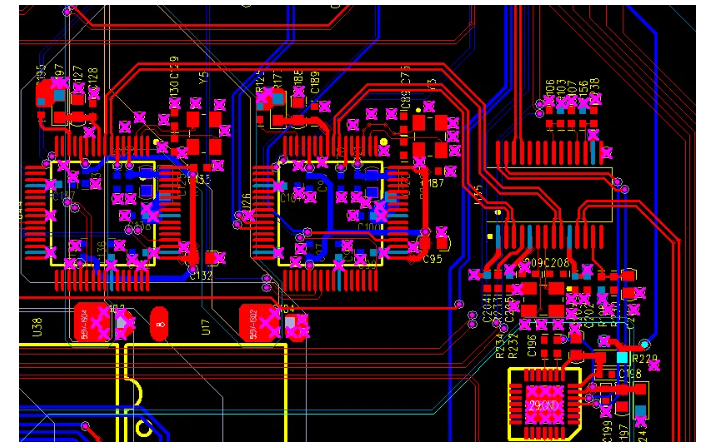

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

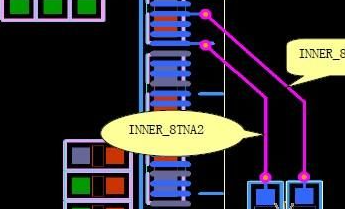

答:PCB设计中有一些信号组需要进行等长处理,以保证组内信号时序要求。第一步,点击Setup-Constraints-Constraint Manager选项,调出规则管理器,如图6-269所示;

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。

PCB设计,遇到差分线,需要做等长设计时,该怎么操作呢?在做走线等长设计的时候,我一般都是采用让走线进入蛇形走线模式,然后走出蛇形线来快速完成等长设计。

Altium Designer 21在之前版本的基础上对蛇形等长功能进行了优化,大大提高了设计的效率和规范性,具体改进可以参考以下说明。1.1新增两种等长样式 在之前的版本设计当中,等长设计时只有单一的U形等长。Altium Designe

购买的4片DDR3 T点拓扑高速pcb设计速成实战视频中没有支路的等长视频,视频中只是说书有讲,但是书上讲的不是很详细,支路的等长我还是不太会吖,能否录个支路的等长视频给我,能否录个from to的用法视频

在高速设计中,基于时序的考虑通常要对信号做线长匹配。对于Allegro PCB设计者来说,我们在等长的时候经常会提到X-NET,利用X-NET功能我们能够很快的计算多点拓扑结构等长长度,并且还能够计算数据组等长误差,很是方便,但是我发现在给很多学员教学的过程中,很多人不清楚这个功能的使用,那么我们这次抽时间弄成一个专题来详细的给大家讲解一下。

扫码关注

扫码关注