- 全部

- 默认排序

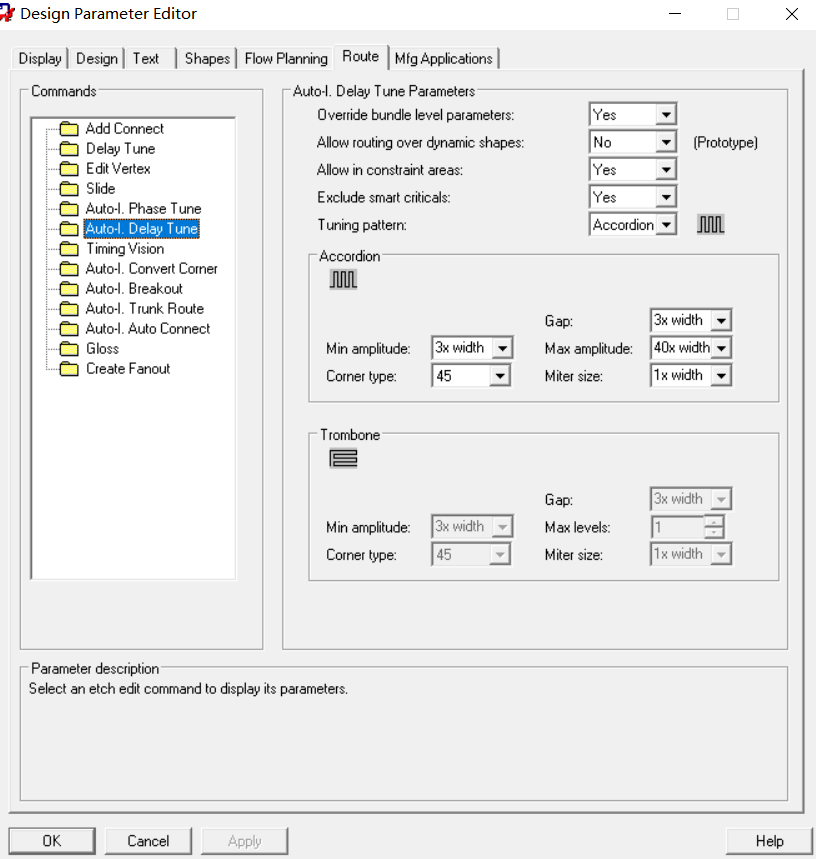

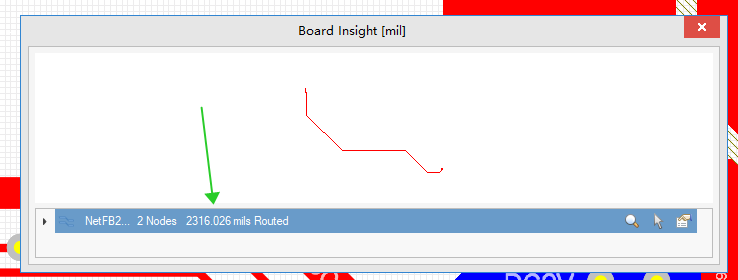

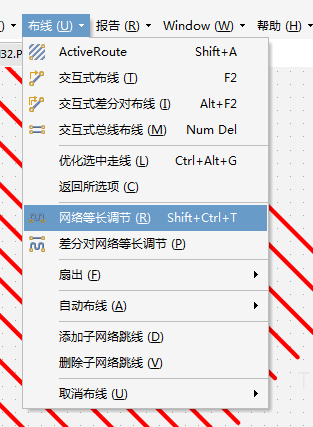

对于一些并行传输的数据而言,需要做到信号同步,以满足时序关系,如果信号的延时相差太大,可能会导致数据无法正确识别,此时就需要进行等长绕线处理。在布线空间较为充足的情况下,自动等长绕线工具能实现自动绕线(delay tune)。但在绕线前,必须把各种规则设置好,建议添加以下规则。

SDRAM信号线等长处理

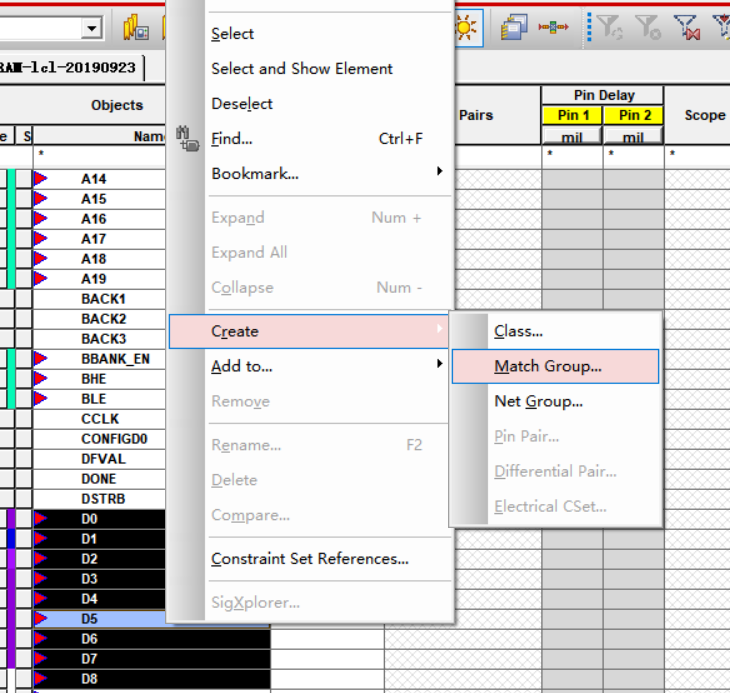

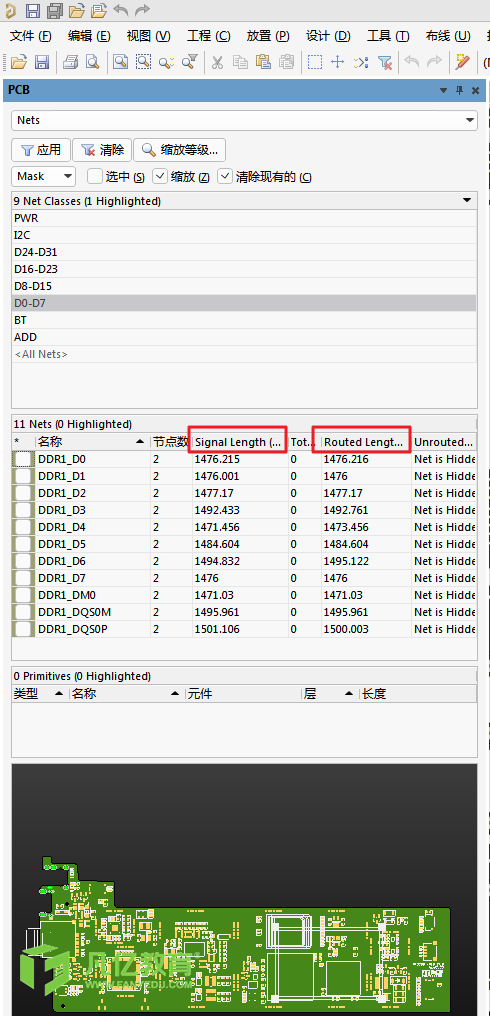

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

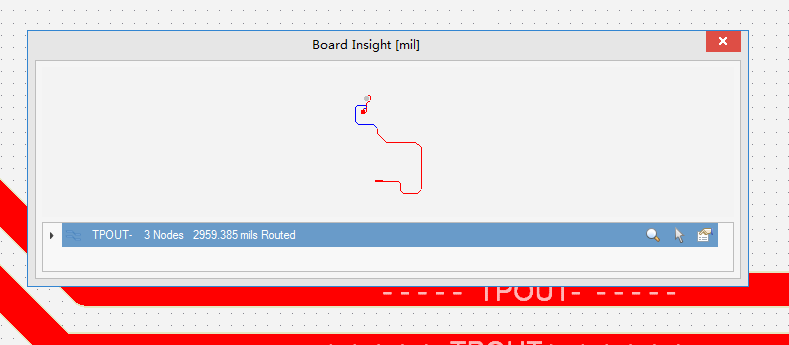

在使用Altium Designer画PCB时,等长布线后,使用快捷键R+L检测布线长度时,发现布的线长不一致,在PCB的nets里查看长度时看到了Signal length和Routed length

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

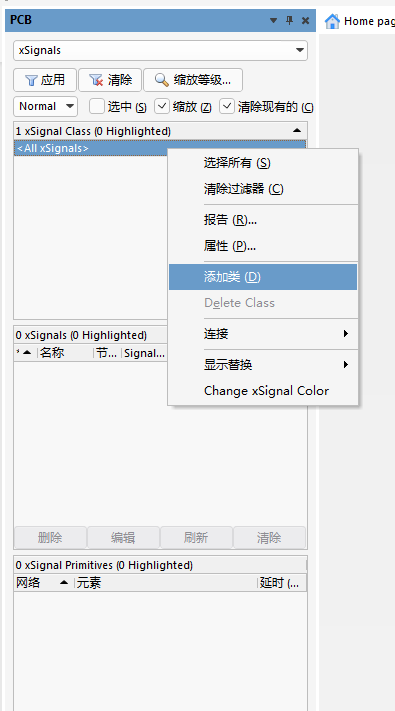

利用Xsignals向导即可自动进行高速设计的长度匹配,它可以自动分析T形分支,元件,信号对和信号组数据,大大减少了高速设计配置时的时间消耗。

答:在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异。高速信号有效的建立保持窗口比较小,要让数据和控制信号都落在有效窗口内,数据、时钟或数

扫码关注

扫码关注