- 全部

- 默认排序

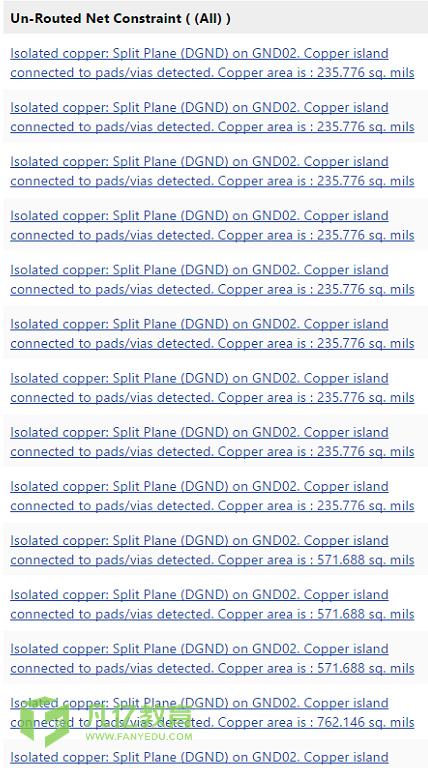

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。比如今天要讲解的DRC报错中的“Isolated copper:Split pllane....”的报错,为了方便大家了解这项报错,我们找到了素材图片如下:

Altium Designer的原理图设计导入PCB,存在两种方法:一种是直接导入法,类似于Allegro的第一方导入;另一种是间接法,即网表对比导入法。

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。

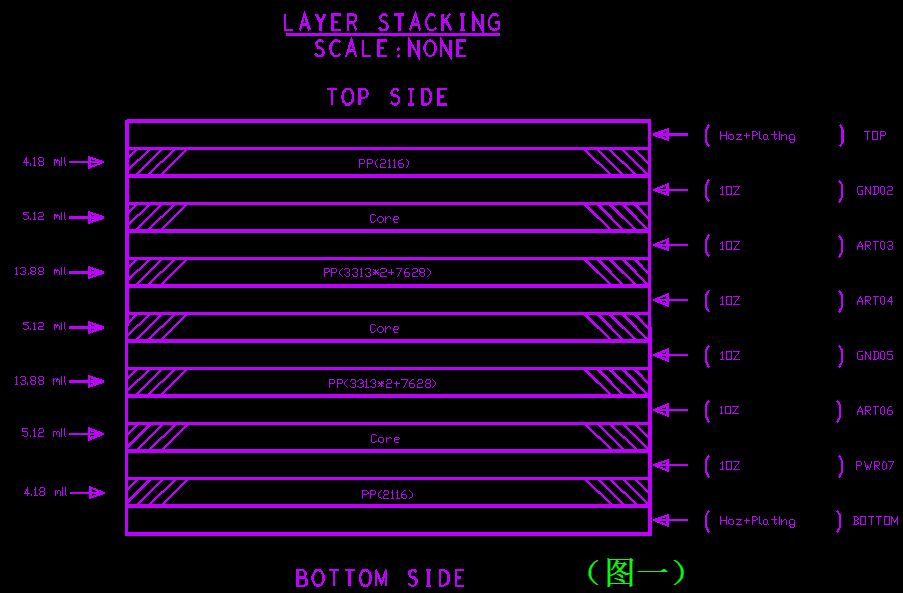

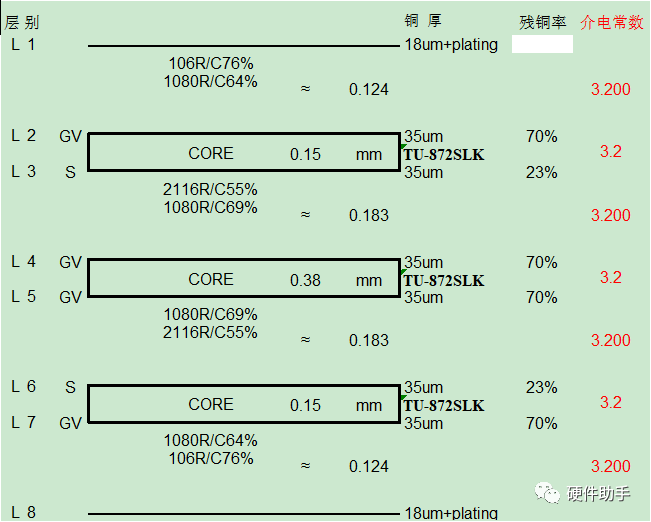

常见的一些叠层文件的形式多种多样,给出的方式也多样化,有的通过excel形式给出,有的通过制板说明文件给出,有的直接放在PCB设计文件中,通过Gerber文件给出。不管是哪种方式,其目的都是为了让设计人员有据可依,能设计出满足功能性能要求的PCB,让生产加工人员能制造出满足设计性能的PCB。 下面这种是将所有的信息都直接放在PCB设计中,并且生成Gerber文件一起提交到工厂。

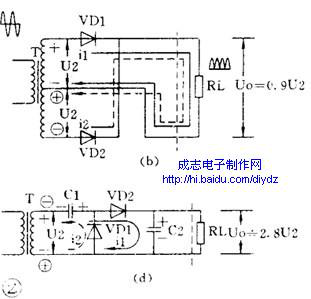

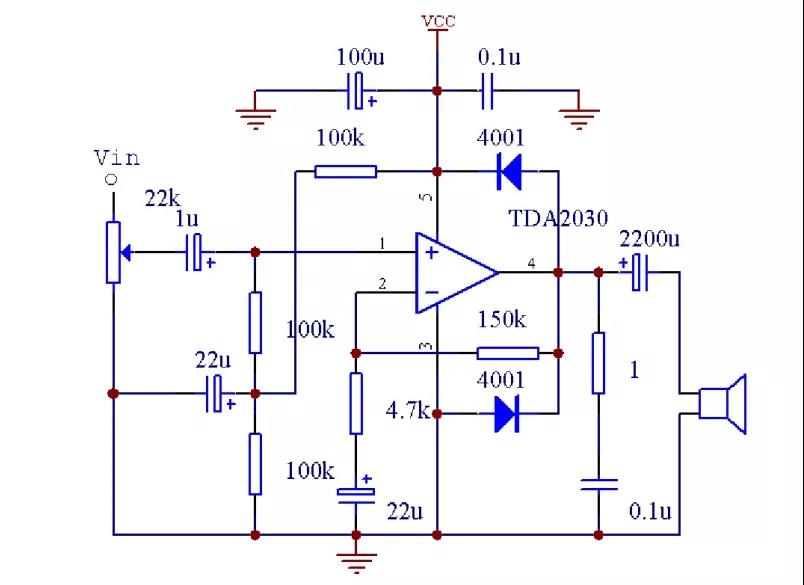

一张电路图通常有几十乃至几百个元器件,它们的连线纵横交叉,形式变化多端,初学者往往不知道该从什么地方开始,怎样才能读懂它。其实电子电路本身有很强的规律性,不管多复杂的电路,经过分析可以发现,它是由少数几个单元电路组成的。

扫码关注

扫码关注