- 全部

- 默认排序

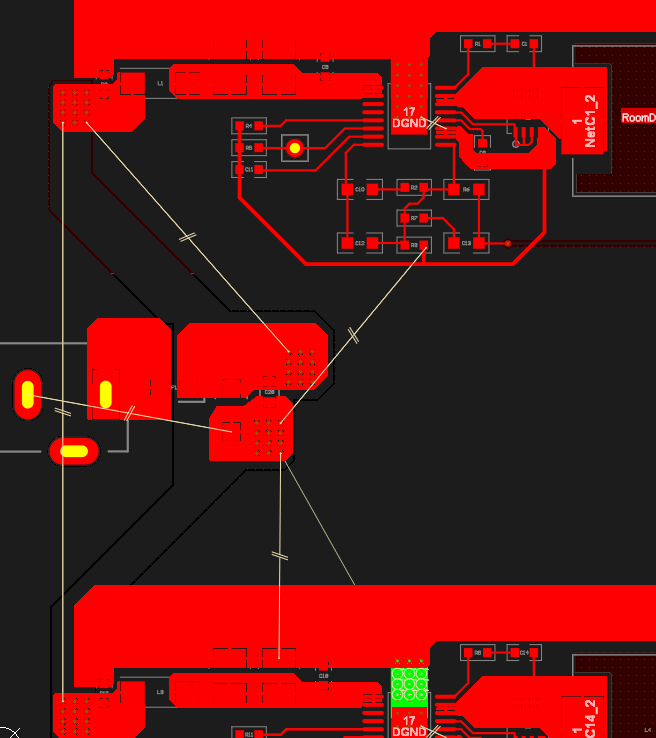

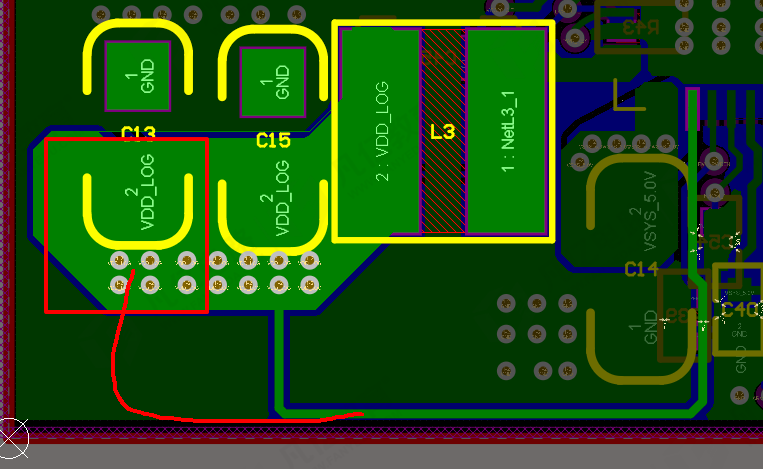

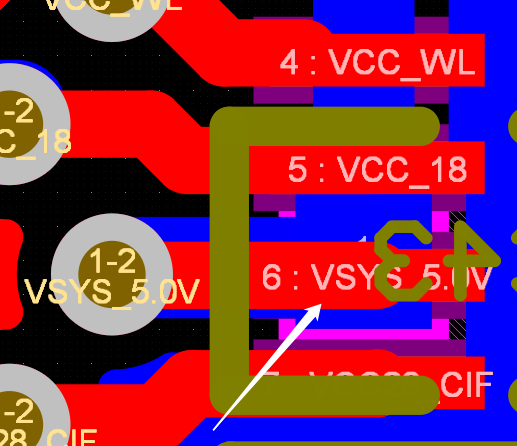

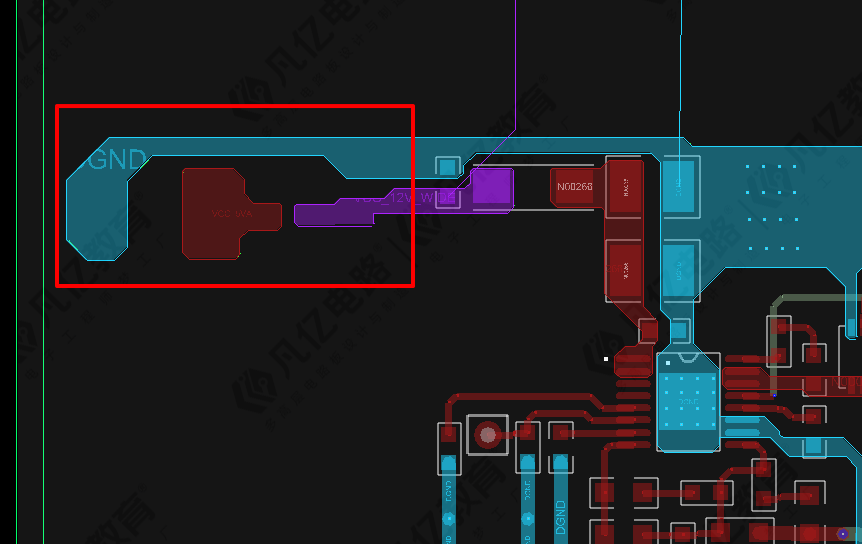

还存在飞线,网络没有连接完全:12V电源信号都没有连接上:铺铜尽量不要直角,钝角铺铜,优化下:电感内部挖空的区域是除了焊盘的区域:此处焊盘出线必须拉出焊盘再去拐线,不能直接从中心拉下来:此处还都是短路报错,自己检查下:除了IC焊盘上的过孔开

过孔打到最后一个器件后方,反馈信号连接到最后一个器件后方电源走线加粗走线同层器件中间多余铺铜挖空走线铺铜在焊盘内和焊盘保持等宽,出焊盘后尽快加粗走线多处尖岬铜皮未处理以上评审报告来源于凡亿教育90天高速PCB特训班作业评审除芯片下方散热打孔

在电源模块设计领域中,很多客户要求产品必须高可靠,为了确保电源模块在各种复杂环境和应用条件下都能稳定运行,那么如何做?今天本文将讲讲如何从多个维度来考虑和优化,希望对小伙伴们有所帮助。1、防浪涌保护电路设计浪涌电流可能会对电路中的元器件造成

走线不要宽过焊盘,拉出焊盘后在加粗散热过孔背面要开窗处理这个线头要删掉这里检查一下是否满足载流以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao

下方电路多余铜皮修掉尽量单点接地,把gnd焊盘连接到一起只在芯片下方打孔器件布局太乱,相邻器件朝一个方向放置中心对齐反馈信号走线8-10mil就可以 电路主输出路径加大载流,这里铜皮加宽以上评审报告来源于凡亿教育90天高速PCB特训班作业评

Verilog,作为底层汇编语言之一,一直以来是许多开发人员的必学编程语言之一,要想硬件设计优秀,做到功能的正确实现,就必须写好高质量的Verilog代码,那么如何确保自己的Verilog代码是优秀的?1、标准化设计确保模块设计符合协议标准

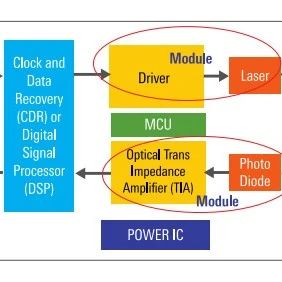

概要多年来,电源模块一直是工程师的最佳选择。它们的优势始终包括减少电路板空间、缩短产品上市时间和较高的一次通过成功率。如今,工程师们在时间和空间方面都受到了全方位的挤压。开发周期缩短,可用于功率传输的空间不复存在,而负载电流却在不断增加。这些趋势推动了功率模块市场的大幅增长。电源模块设计方面的技术进

米思齐(Mixly)是一款专为单片机设计的图形化编程工具,通过拖拽模块替代复杂代码,让初学者快速实现LED控制、传感器交互等基础功能。本文聚焦其核心特点与实战应用,助你高效入门单片机开发。一、核心功能与优势1、图形化模块设计模块分类:涵盖输

PCB层数直接影响电源模块的稳定性与效率。本文从单层到多层PCB板的结构特性出发,提炼电源模块设计的核心差异与实操要点。一、单层PCB电源模块设计布局紧凑性元器件需集中布置,缩短电源线长度关键路径(如电感、MOSFET)采用最短走线电源线宽

射频模块的性能与PCB层数设计密切相关。不同层数的PCB在信号完整性、电磁屏蔽、阻抗控制等方面存在显著差异。下面将简谈这不同层数的PCB板射频模块设计。1、双层板(2层)信号层与地平面:顶层为信号层,底层为完整地平面,避免跨层走线。射频线宽

扫码关注

扫码关注