- 全部

- 默认排序

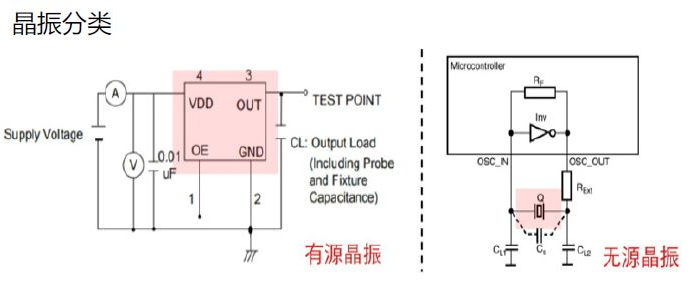

晶振相当于人的心脏,能跳动,整个系统才是“活的”。晶振常见有有源晶振、无源晶振。有源晶振比较贵,但是需要外围电路少,供个电就能工作。无源晶振价格便宜,匹配电路复杂些。以无源晶振进行分析,以下是无源的参数信息,频率FL、load电容CL、频偏

高通晶振设计指导

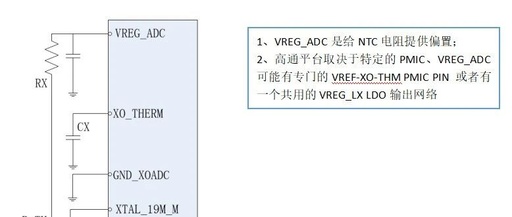

前言:1、随着目前PCB越来越小,越来越薄,导致更加严重的散热问题2、XTAL_IN/XTAL_OUT和GND_LINE可以作为热源的传热路径,导致GPS/GNSS受到影响。3、布局区域约束要求晶振布局必须靠近PMIC 一、布局要求1、晶振需要远离PMIC,需要保证XTAL_IN/OUT的距离在3~

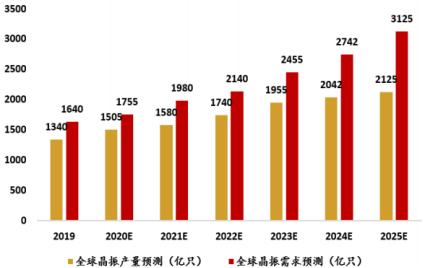

晶振作为频率控制和频率选择基础元件,广泛应用于资讯设备、移动终端、通信及网络设备、汽车电子、智能电表、电子银行口令卡等领域,随着新兴电子产业、物联网的快速发展,及以 5G、蓝牙 5.0、Wi-Fi 6 等无线通信新技术的广泛应用,预计全球

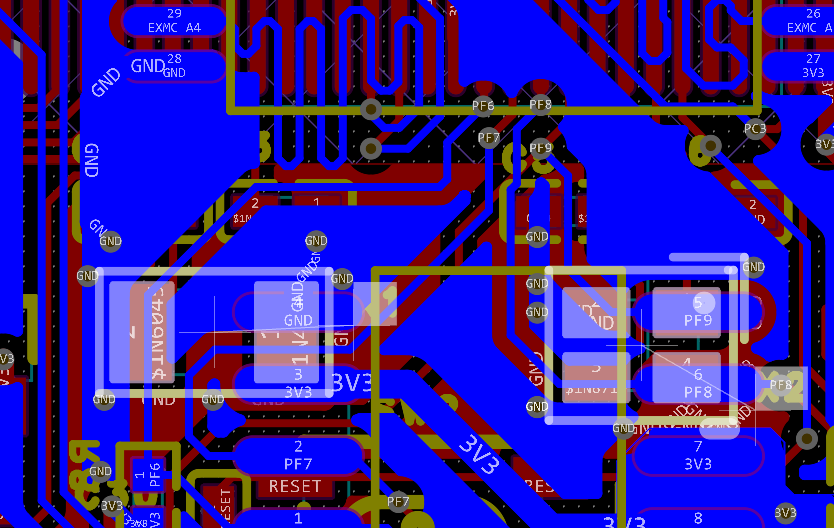

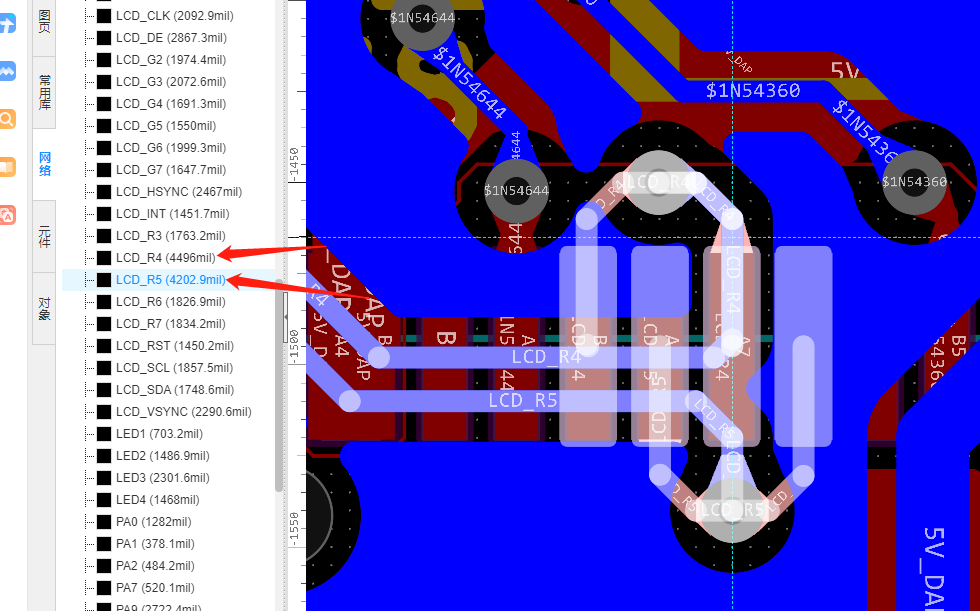

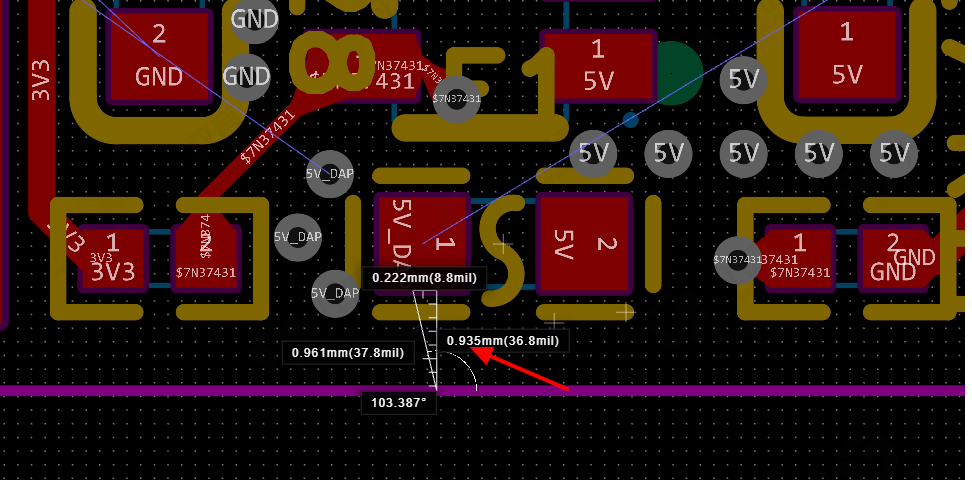

晶振下面尽量不要走线2.晶振需要走类差分形式3.电源的输入输出需要铺铜处理,铺铜宽度需要满足电源电流大小4.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍5.时钟包地的地线上需要间隔150mil-200mil打上一个过孔6.焊盘出线

晶振下面尽量不要走线2.线宽突变,确认一下具体线宽,尽量保持统一3.电源输入的滤波电容应该靠近输入管脚(4脚)放置4.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍5.注意等长线之间需要满足3W规则6.走线尽量不要有直角,此处需要优

器件摆放注意对齐处理处理2.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍3.此处走线需要优化一下,尽量从焊盘长边出线4.焊盘出线不规范,焊盘中心出线至外部才能拐线处理,避免生产出现虚焊5.晶振下面尽量不要走线6.线宽突变,确认一下

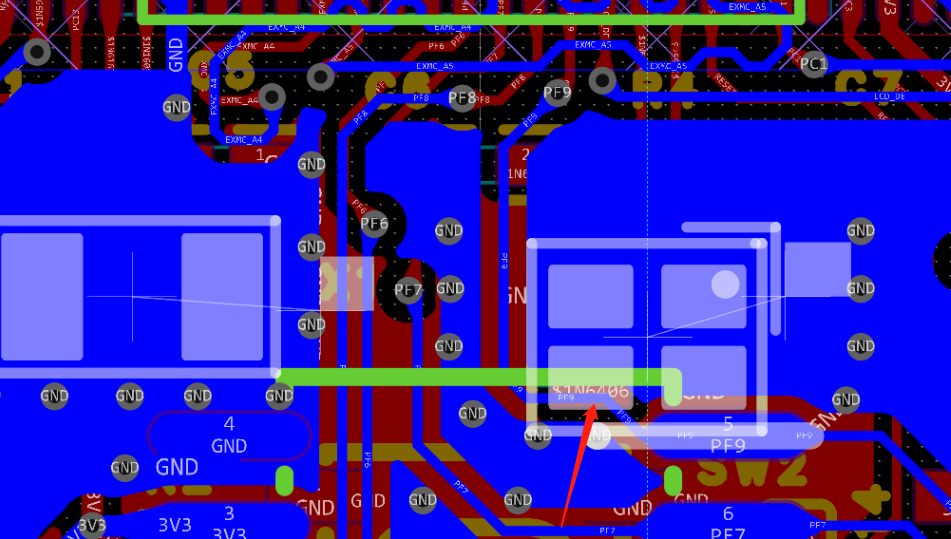

差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍2.器件摆放尽量对齐处理3.晶振走线需要走类差分处理4.电源输入的滤波电容应该靠近输入管脚(4脚)放置5.此处在一层走线即可,建议铺铜处理6.时钟包地需要在地上间隔150mil-200m

晶振下面尽量不要走线2.差分线处理不当,锯齿状等长,凸起高度不得超过线距的两倍3.器件摆放尽量对齐处理4.电源输入的滤波电容应该靠近输入管脚(4脚)放置5.此处一层连通无需打孔6.线宽突变,确认一下具体线宽,尽量保持统一7.时钟包地上间隔需

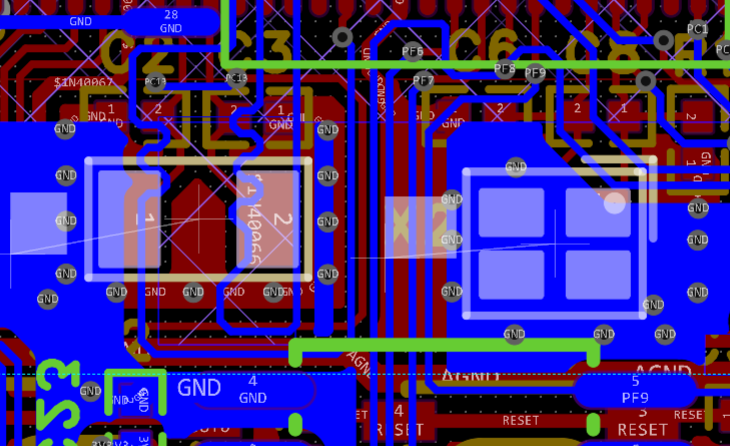

USB的差分信号需要进行对内等长,等长误差为5mil2.晶振走线需要走类差分处理3.此处是用菊花链的方式进行等长,建议使用创建焊盘对组进行分段等长(U1-U2,U2-FPC1)4.电源输入的滤波电容应该靠近输入管脚(4脚)放置5.电源输出部

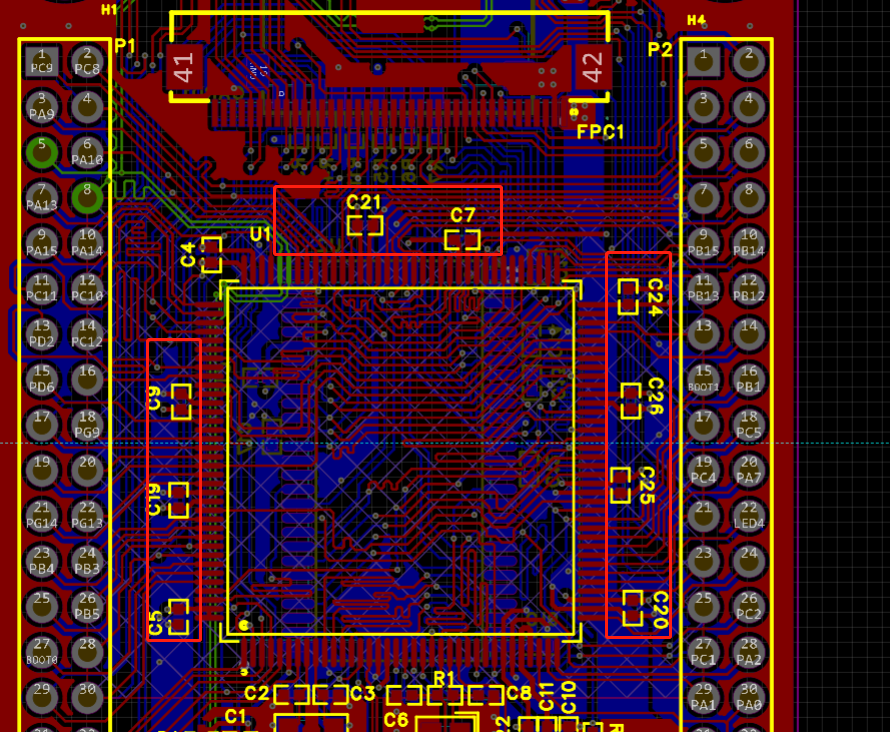

梁山派pcb设计特训营作业评审要求器件离板边5mm不要布局器件,除非特殊要求或后续板子设计可以添加工艺边。 【问题改善建议】:在贴片时留给设备的传送带固定用,建议无特殊要求板边5mm不要布局器件。2.晶振布局、布线错误。 【问题改善

扫码关注

扫码关注