前言:

1、随着目前PCB越来越小,越来越薄,导致更加严重的散热问题

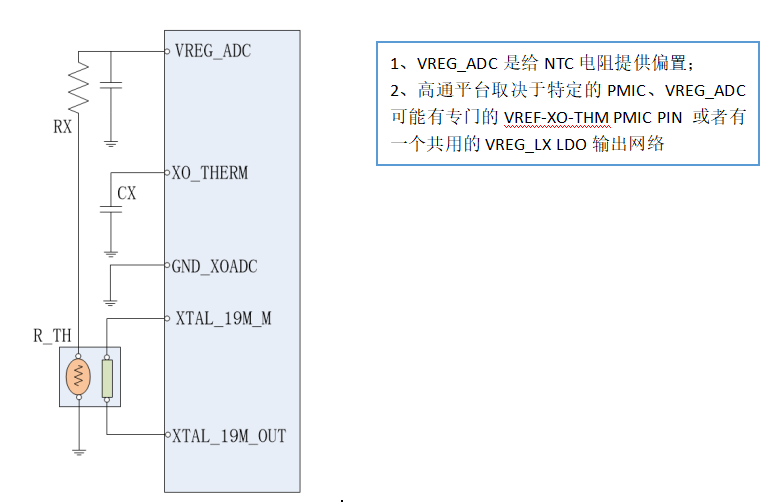

2、XTAL_IN/XTAL_OUT和GND_LINE可以作为热源的传热路径,导致GPS/GNSS受到影响。

3、布局区域约束要求晶振布局必须靠近PMIC

一、布局要求

1、晶振需要远离PMIC,需要保证XTAL_IN/OUT的距离在3~10mm

2、验证XTAL距离PA和MSM/MDM/APQ/QCA距离1mm(在同一层时),不能布局在PA/MSM/APQ/QCA等IC的背面

3、需要隔离可能影响到GNSS性能的主要热源

二、布局指导

布局指导

1

热隔离对GNSS的性能非常重要

2

晶振下方净空至少2层

3

GND_XOADC网络除了主地外禁止连接到其它地网络

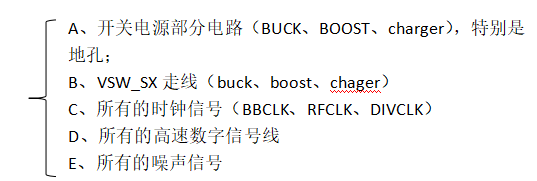

三、走线checlist

走线checklist

1

晶振和XTAL_IN/XTAL_OUT至少净空2层

2

XTAL_IN/OUT

1、XTAL_IN/OUT走线长度为3~10mm

(1) XTAL如果距离PMIC较近,XTAL_IN/OUT路径应当弯曲增加线长;

(2) 在高通某些平台中,会把时钟部分从PMIC中摘出来,此时XTAL_IN/OUT的路径应该尽可能的短;

(3) XTAL_IN/OUT 的走线宽度<3mil<>

(4) XTAL_IN/OUT尽量走在最表层

2、XTAL_IN/OUT不需要走差分线

3、XTAL_IN/OUT之间没有必要加隔离地

4、XTAL_IN/OUT的走线过长,会导致PMIC无法调节寄生电容

5、XTAL_IN/OUT过短,GNSS的性能会受到PMIC热源影响

扫码关注

扫码关注