- 全部

- 默认排序

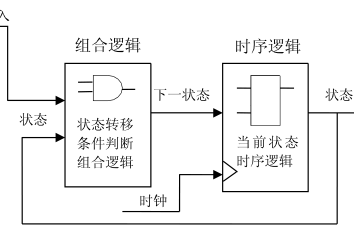

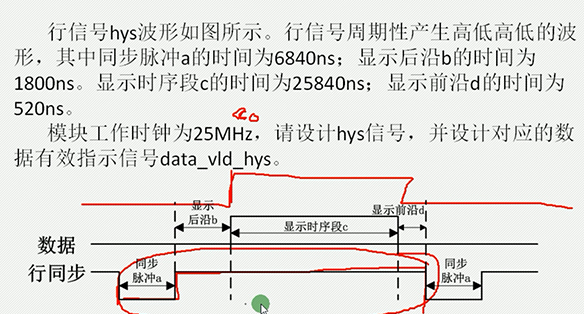

在FPGA设计里,状态机的设计是最为重要的环节之一。很多FPGA系统里的运行成功基本上和状态机设计相关,毫不夸张地说,FPGA系统的成功,其中一半归于状态机。所以我们该如何做好状态机?一般来说,工程师在状态机的设计中基本采用两段式写法(2个

FPGA和CPLD都属于可编程逻辑器件,有着很多共同特点,但由于FPGA和CPLD的结构差异,所以它们的区别也很大,所以本文将详谈FPGA和CPLD的区别及联系。1、CPLD更适合完成各种算法和组合逻辑,FPGA更适合完成时序逻辑。换句话说

可编程逻辑器件是一种集成电路,可根据用户的需求和编程指令来执行特定的逻辑功能。这些器件在数字电子系统中扮演着重要的角色,能够实现逻辑门、组合逻辑电路以及时序逻辑电路等功能。基本结构方面,可编程逻辑器件通常由以下几个主要部分组成:输入/输出端

扫码关注

扫码关注