- 全部

- 默认排序

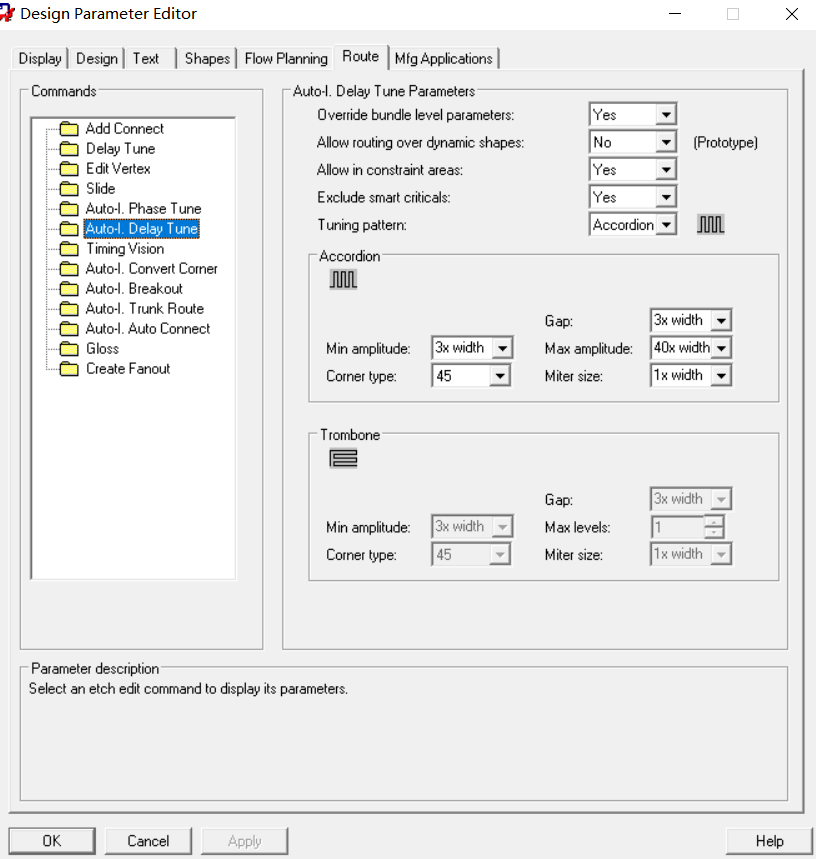

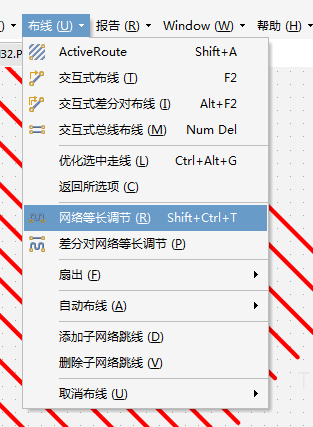

对于一些并行传输的数据而言,需要做到信号同步,以满足时序关系,如果信号的延时相差太大,可能会导致数据无法正确识别,此时就需要进行等长绕线处理。在布线空间较为充足的情况下,自动等长绕线工具能实现自动绕线(delay tune)。但在绕线前,必须把各种规则设置好,建议添加以下规则。

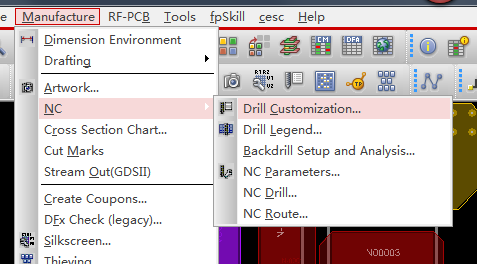

钻孔表格的设置与生成

任何pcb设计文件设计完成后,都需要通过相关功能输出生成所需要的文件资料,allegro软件的功能确保了pcb的设计数据与成产文件完全一致,从而可以直接在设计界面中输出所有pcb生产、测试、装配所需的文件,以下要将的是pcb钻孔表格的设置与生成

SDRAM信号线等长处理

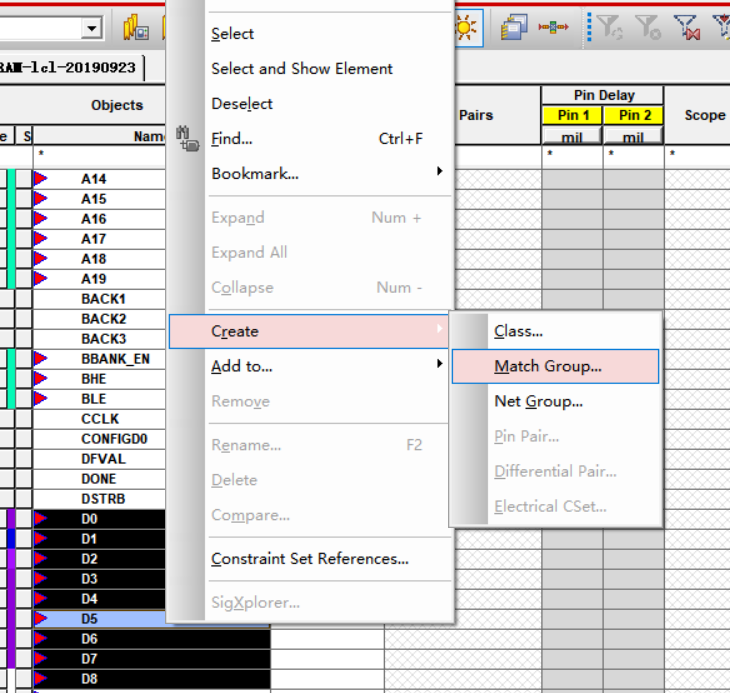

在布线完成后,这里以SDRAM为例,要对SDRAM信号线进行等长处理,以满足时序要求。SDRAM的信号可分为数据线、地址线、控制线、时钟线,走线时要同组同层,间距满足3W原则,每组数据线的等长误差范围为+-50mil,地址线、控制线、时钟线的等长误差范围为+-100mil。

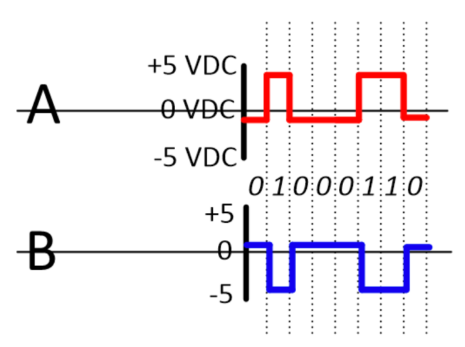

RS485作为常见的总线之一,几乎每个工控设备都在用,我们也对其熟悉不过了。我们都知道RS485双半双工通信,其CPU内部的根源是串口通信,串口通信是区分发送TX和接收RX的,在同一对差分信号线上同时传输TX、RX,就是进行方向的控制,方向的控制时机不对,数据传送是要出问题的。

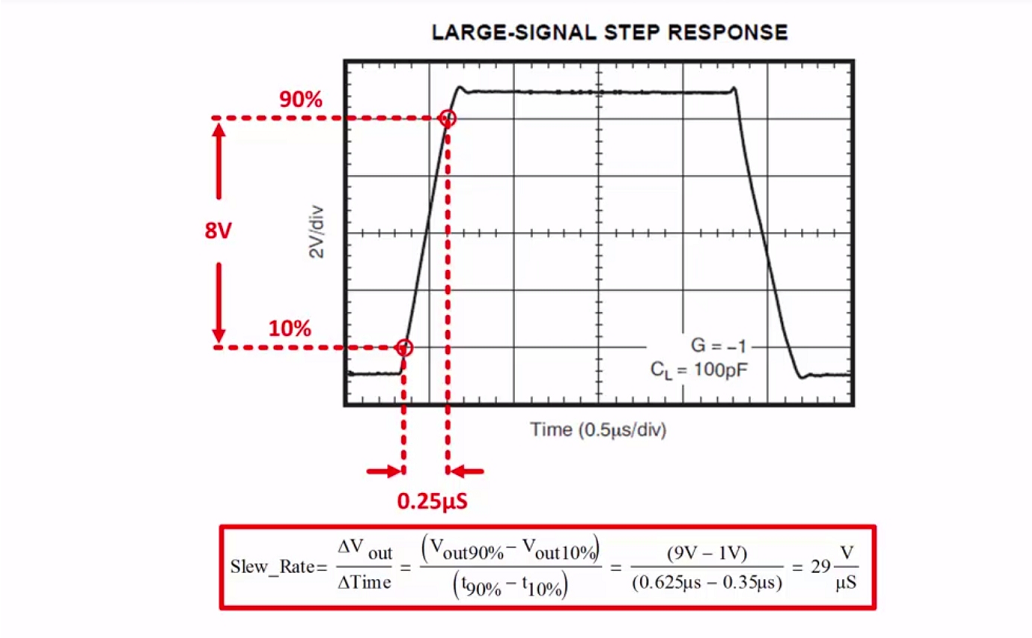

运放的压摆率

压摆率定义为运放输出电压可以达到的最大摆动速率,它以伏每微妙为单位,测量压摆率的时候可以在输入端放置一个较大的阶越信号,比如1V的伏值,然后测量输出端的电压摆动,也就是图中输出量从10到90的时间间隔,我们可以看下我们的这个0.25us,有些对应的数据手册中会对应给出压摆率的对应的指标,有些会用大信号的阶越信号来代替

鸿蒙OS开发学习教程

鸿蒙OS开发学习教程HML语法页面结构和html相同的标签嵌套,最外层是div数据绑定与vue用法类似hml:{{ 变量名 }}js:变量放在data中export default{ data:{ 变量名: value }}事件绑定类似v-on(在js中绑定的函数和data同级)hml: 或 js:放在data后:export default{

电子设计当中,经常用到差分走线,如USB的D+与D-差分信号,HDMI的数据差分与时钟差分等。虽然现在很多设计者都是在PCB中添加差分,但是还是有许多设计者习惯在PCB中就添加好差分。那么,如何在原理图中添加差分标识呢?

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

扫码关注

扫码关注