- 全部

- 默认排序

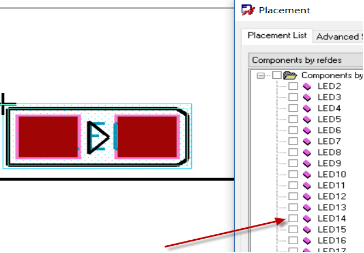

答:这里所说的Assign RefDes功能,就是为复制的假的元器件进行编号的指定,一般用于LED灯板这类很多相同的模块的PCB板的设计中,具体操作的步骤如下所示:第一步,这些假的器件必须是要后台存在的,没有放置在PCB中,如图5-226所示;

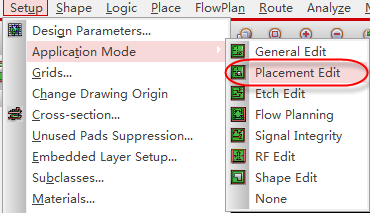

答:我们在使用Allegro进行PCB的绘制时,有时候需要将整个模块放置到背面去,也就是进行镜像,镜像的不仅仅是器件,还有走线、过孔等元素,这里我们就介绍一下,在Allegro软件如何将一个做好的模块,整体镜像到另一面,具体操作如下:

答:很多刚开始接触这个Allegro软件的同学,就有这样的疑问,我的原理图的网表都已经导入到PCB中了,为什么PCB板上什么都没有呢?元器件、飞线等都没有。其实,只要是网表导入到PCB中,器件都是在后台显示,需要指定元器件封装库,然后手动放置出来,下面我们详细介绍一下操作的办法:

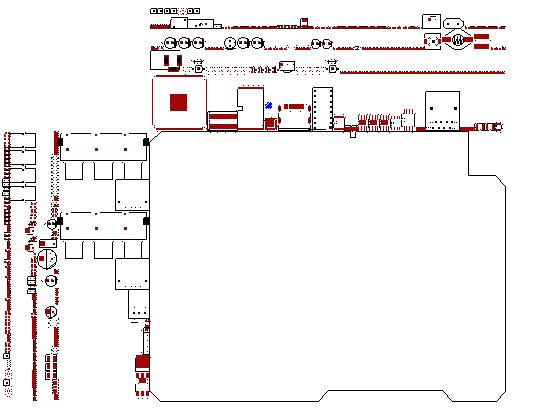

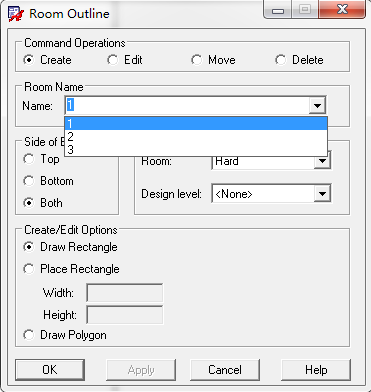

答:上述我们讲解了怎么快速的将元器件放置在PCB板上,通过图6-40所示的图可以看出,器件放置的都是很零散的,不是按模块或者是按页放置的,这里给大家介绍一些,通过在原理图添加ROOM属性,然后通过ROOM框在PCB板上来放置元器件,这样就可以根据模块或者一页原理图去发放置元器件了,具体操作如下:

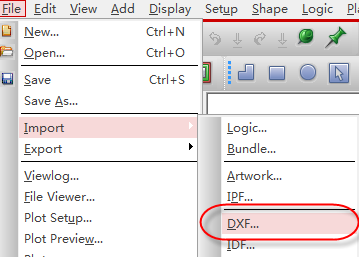

答:我们在进行PCB设计之前,除了将原理图的网表导入,将元器件放置在PCB板上,还需要做的就是将结构文件导入到PCB中,进行结构器件的定位。这里呢,我们详细讲解一下结构文件如何导入到PCB中,具体操作如下:

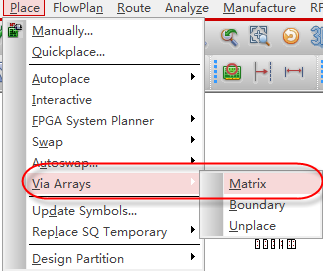

答:所谓的阵列过孔,就是在某一个区域或者走线上,按照某种特定的规律,均匀整齐的放置过孔,执行菜单命令Place-Via Arrays,进行阵列过孔的放置,如图6-121所示,在下拉菜单中有三个选项,具体的含义如下:

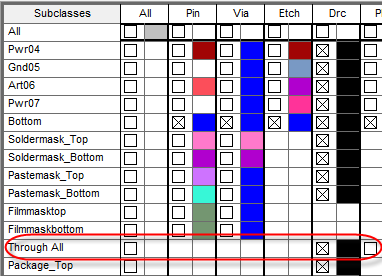

答:我们在PCB设计完成之后,都需要对整板铺地铜处理,然后在铺的地铜上面放置地过孔,但是有这样一个现象,相同的地过孔放重叠了,并不会产生DRC错误,我们应该如何设置,才可以让相同网络的重叠过孔产生DRC错误呢,这里讲解一下,具体操作如下所示:

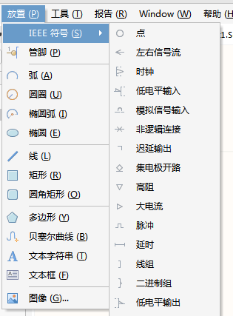

答:AD里面的IEEE符号通常用来表示元件的某个引脚的输入或者输出的属性,便于分析电路图。如图2.14所示是放置下面的IEEE符号。

答:AD在创建原理图器件封装库时,放置管脚的Type的含义是管脚的类型,表示管脚的类型,每一种类型的含义解释如下:Input: 输入信号。作为输入引脚使用

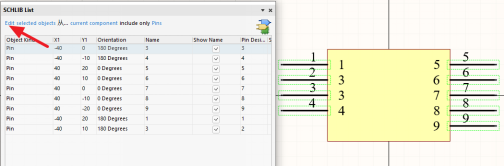

答:针对于管脚数目比较多的IC类元器件,可以先把全部的管脚数目放置出来,然后进行属性的统一修改。操作的步骤如下:

扫码关注

扫码关注