- 全部

- 默认排序

No ERC检查点即忽略ERC检查点,是指该点所附加的元件管脚在进行ERC检查时,如果出现错误或者警告,错误或者警告将被忽略过去,不影响网络表的生成。忽略ERC检查点本身不具有任何的电气特性,主要用于检查原理图

答:AD在创建原理图器件封装库时,放置管脚的Type的含义是管脚的类型,表示管脚的类型,每一种类型的含义解释如下:Input: 输入信号。作为输入引脚使用

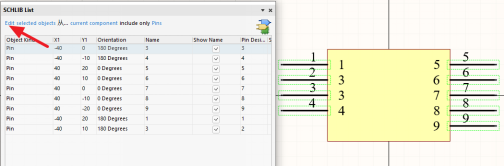

答:针对于管脚数目比较多的IC类元器件,可以先把全部的管脚数目放置出来,然后进行属性的统一修改。操作的步骤如下:

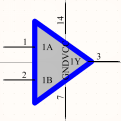

答:对于信号的功能来说有时候需要标注管脚是低电平有效,那么这个负信号标注需要在软件里面进行标注。执行快捷键“PP”,放置管脚,接着选择管脚双击,弹出管脚属性编辑界面。在Name栏填写网络名称的时候,加上“\”,如“E\A\”,如图2.23所示。

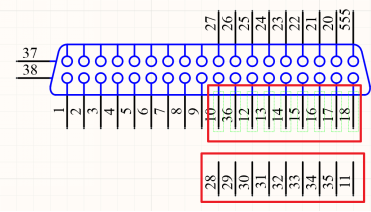

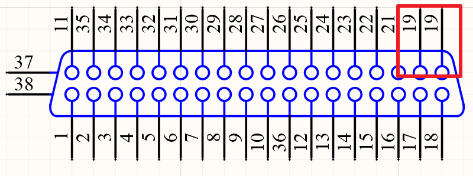

答:在绘制原理图原器件封装的时候,制作一个管脚特别多的原理图原器件封装。需要一个一个的功能模块分开,同功能管脚需要放置到一块。运用批量移动的方法可以节约大量的时间。

No ERC检查点即忽略ERC检查点,是指该点所附加的元件管脚在进行ERC时,如果出现错误或者警告,错误或者警告将被忽略过去,不影响网络报表的生成。忽略ERC检查点本身并不具有任何的电气特性,主要用于检查原理图。 图5-50 放置No E

扫码关注

扫码关注