- 全部

- 默认排序

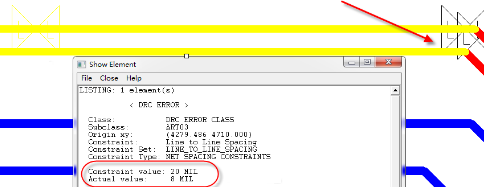

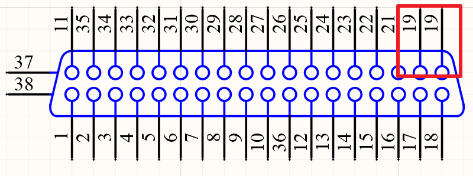

答:我们在PCB设计过程中,差分信号是比较重要的信号,一般设置差分信号到其它信号的间距是20mil,但是设置完差分信号到其它信号的间距之后,差分对内PN之间不满足20mil的间距,会报错,如图6-205所示:

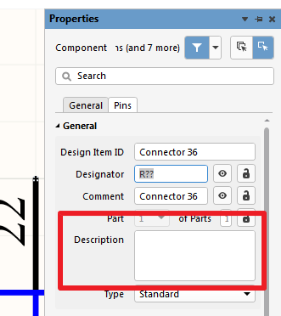

答:在绘制原理图封装的时候,就可以对其进行PCB封装的分配。这样会省去很多的设计时间,而且不容易出错。再倒入到PCB中的时候会少很多的报错。

答:1)当库元件规则检测出“NO Description”的报错时,是因为器件缺少描述。如图2.50所示。

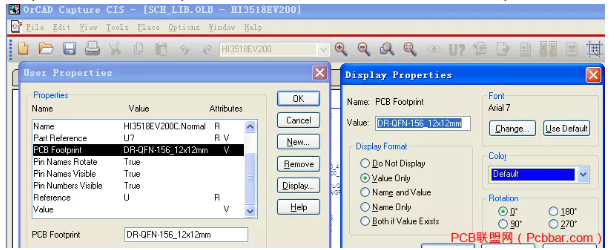

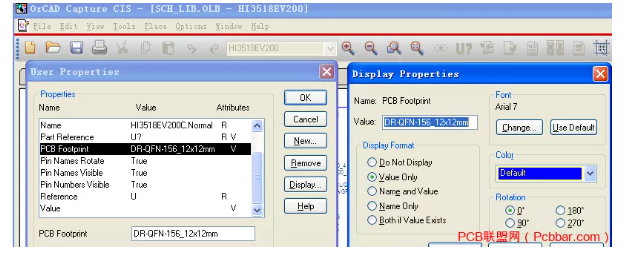

出现的原因:在原理图库中绘制了一个带有多个part的封装(HI3518EV200),但未设置PCB Footprint。在dsn空间的一个原理图内,通过Edit Part修改改器件的PCB Footprint时候,会因为dsn空间内的元器件封装与sch_lib.olb元件库的封装不同,导致会把修改后的封装保存到dsn空间内的Design Cache,并将名字修改为HI3518EV200_x。

出现的原因:在原理图库中绘制了一个带有多个part的封装(HI3518EV200),但未设置PCB Footprint。在dsn空间的一个原理图内,通过Edit Part修改改器件的PCB Footprint时候,会因为dsn空间内的元器件封装与sch_lib.olb元件库的封装不同,导致会把修改后的封装保存到dsn空间内的Design Cache,并将名字修改为HI3518EV200_x。

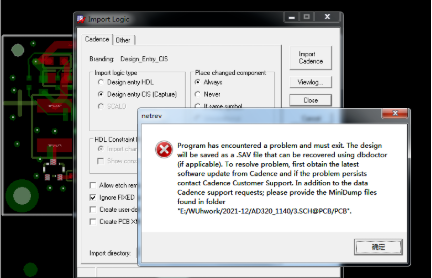

Allegro在导入网表文件时或者运行软件的时候出现如下截图报错,很多网友找不到解决方法,其实是可以根据下面俩种方法去解决这个问题的。第一种:当在设计过程中出现这个问题或者是在刚打开这个某一些文件出现这个问题的时候,可以点击菜单栏命令“To

EFT整改

#凡亿7月星企划#有一个设备A,在做EFT测试时发现,接口A总是通信失败。接口A信号,通过连接的IC处理后,再与设备A的主控通信。观测失败过程,发现每当EFT发送干扰时接口A就会报错。EFT干扰的注入主要是通过叠加在适配器等电源的输入端,

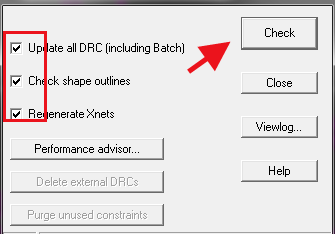

安全间距DRC检查

安全间距DRC检查主要是检查各元素间设计的距离是否小于规则内设置的距离,若小于则会有短路风险,通过DRC检查可以将报错的位置显示出来,方便设计师进行DRC消除。进行安全间距DRC检查前,建议大家先把铜皮处理好,把所有电气层打开,将PCB整板

Allegro在导入网表文件时或者运行软件的时候出现如下截图报错,很多网友找不到解决方法,其实是可以根据下面俩种方法去解决这个问题的。第一种解决办法:1、当在设计过程中出现这个问题或者是在刚打开这个某一些文件出现这个问题的时候,可以点击菜单

扫码关注

扫码关注