- 全部

- 默认排序

一个完整的原理图文件,需要发给别人查看某一个模块原理图或某一页原理图时,为了原理图文件的保密性考虑,可以利用软件输出PDF格式的文件,方便别人进行查阅。通过视频中的讲解一起来学习下logic软件怎样导出PDF格式文件。

在logic软件中绘制原理图,添加元器件可能有些器件在制作时并没有添加value值的属性,那我们添加到原理图当中后怎样来添加,怎样来进行器件批量value值的显示与隐藏。

在logic软件中绘制原理图,添加元器件后有些器件默认会显示器件的管脚名称、管脚编号、元件类型等信息,那怎样来进行隐藏,怎样对板上的器件进行批量属性显示与隐藏操作。

在Logic原理图中对元件已经分配好了封装,但后面要对封装进行更换,要怎样去进行这个操作,视频当中讲解了两种更改PCB封装的方法,和更改后不行的解决办法。

在Logic原理图软件中,同一页面的连接关系处理有两种方式:一种是直接连线的方式,一种是放置网络编号的方式使其连接在一起,视频中对添加方法进行演示和讲解。

我们在制作元件类型时,有些器件没有给分配封装,那在后面绘制原理图时,对于这种没有分配好封装的器件,我们怎么单个去进行封装分配 ,操作步骤很简单,视频当中有详细讲解。

PADS Logic软件提供了元件库管理、原理图设计、原理图符号创建向导、元器件浏览和检索、物料清单输出、ECO同步和网表输出等功能,是一个界面友好、操作简单且功能齐全的原理图设计软件。

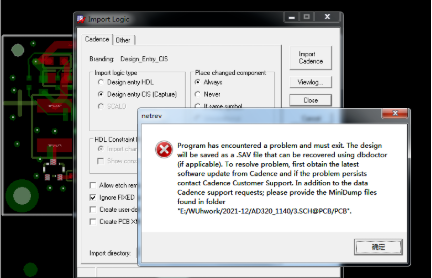

Allegro在导入网表文件时或者运行软件的时候出现如下截图报错,很多网友找不到解决方法,其实是可以根据下面俩种方法去解决这个问题的。第一种:当在设计过程中出现这个问题或者是在刚打开这个某一些文件出现这个问题的时候,可以点击菜单栏命令“To

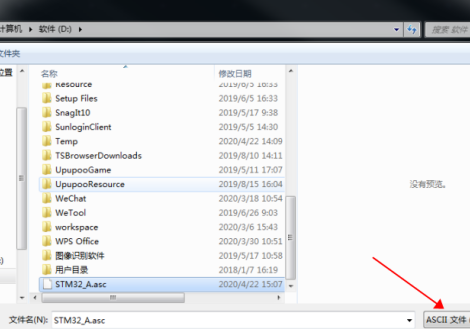

PADS Layout导入网表,即将原理图与PCB进行同步,具体步骤可参考“4.6.1 PADS Logic与layout同步操作”内容。除了导入Logic原理图文件,还可将Orcad原理图导出的ASC文件导入到Layout内。1)执行菜单

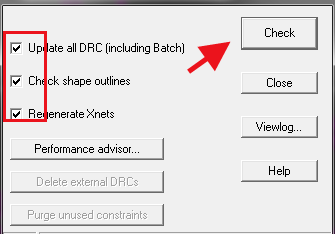

Allegro在导入网表文件时或者运行软件的时候出现如下截图报错,很多网友找不到解决方法,其实是可以根据下面俩种方法去解决这个问题的。第一种解决办法:1、当在设计过程中出现这个问题或者是在刚打开这个某一些文件出现这个问题的时候,可以点击菜单

扫码关注

扫码关注