- 全部

- 默认排序

在Altium Designer中我们经常会遇到一些接触的连接,但是DRC检查开断路的时候是查不出来的但是往往这个接触不良的连接会使后期生产出来的板出现开路的现象。像这种现象我们怎么去避免呢?

大家好,我是龙学飞,欢迎大家学习我的本套课程,这套课程主要给大家介绍基于Realtek RTL8306平台路由器产品4层PCB设计的全过程,包括PCB设计预处理---PCB设计分析---PCB原理图、结构导入---PCB布局处理---PCB设计规则添加---PCB设计布线处理---PCB设计等长处理---电源平面分割处理---丝印调整---DRC检查---GERBER输出---文件归档等PCB设计的整个流程,通过学习本视频,可以迅速地掌握4层初等难度PCB设计方法及思路。

本视频采用Altium designer 19,分享关于缝合地过孔的添加,缝合地过孔添加出现问题,缝合地过孔的放置条件,和缝合地过孔的移除,缝合地过孔的区域放置,缝合地过孔的界面的认识。

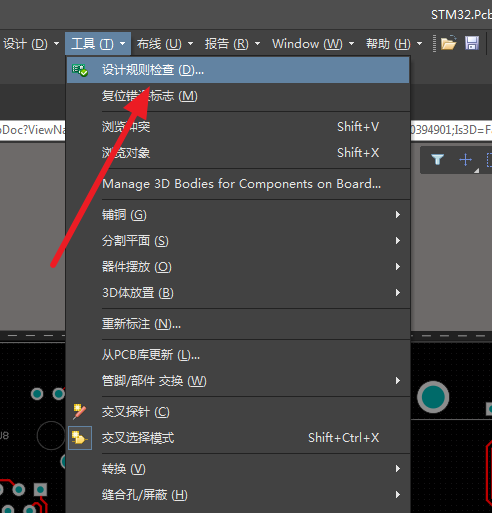

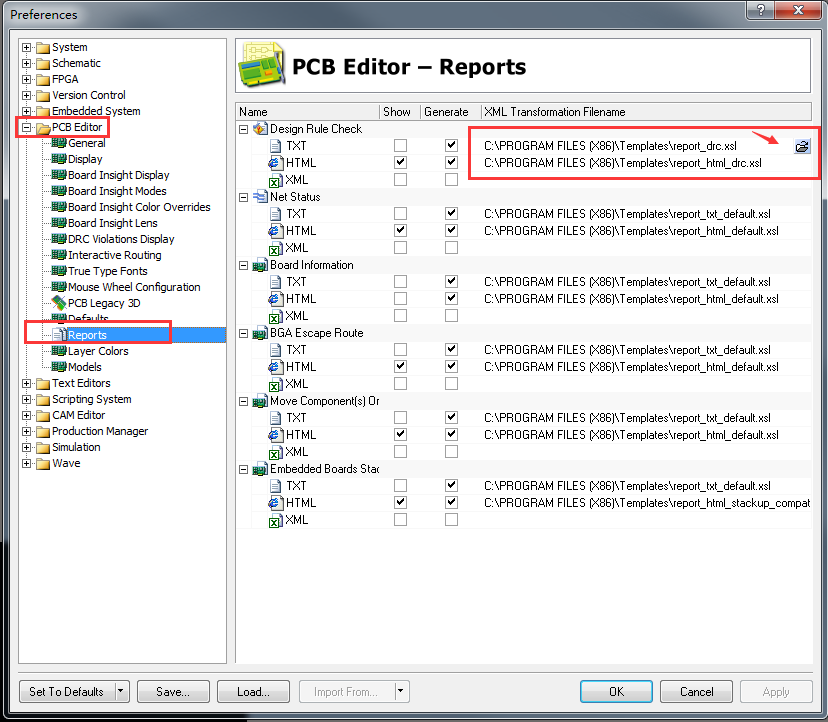

在设计PCB的时候,为了满足各项设计要求的原因,我们需要设置很多的约束规则,然后设计完成之后,去进行DRC检查。DRC检查就是检查我们的PCB设计是否满足所设置的规则,常见的DRC检查有开路,短路,间距等等规则约束。接下来我们就来讲讲常见的DRC设置有哪一些。

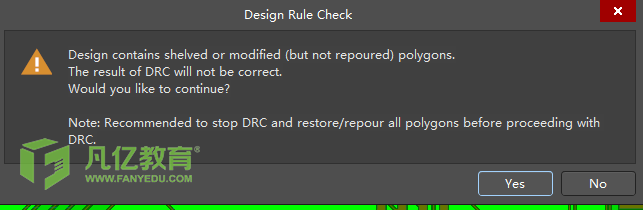

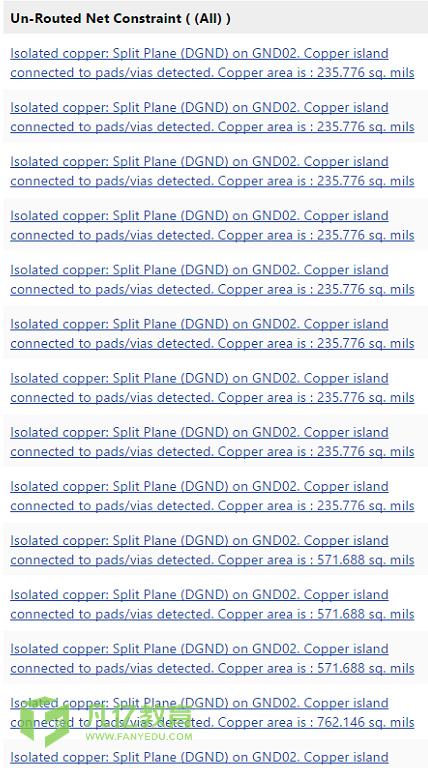

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。比如今天要讲解的DRC报错中的“Isolated copper:Split pllane....”的报错,为了方便大家了解这项报错,我们找到了素材图片如下:

前期为了满足各项设计的要求,我们会设置很多约束规则,当一个PCB单板设计完成之后,通常要进行DRC(Design Rule Check)检查。DRC检查就是检查设计是否满足所设置的规则。一个完整的PCB设计必须经过各项电气规则检查。常见的检查项包括间距、开路以及短路的检查,更加严格的还有差分对、阻抗线等检查。

我们在进行PCB设计的时候,最后我们需要去进行DRC的检查,检查完成之后会出现各种总各样的报错,当然其中常见的间距报错,规则报错我们都知道怎么更改,也能看懂大概的意思。可以有时候碰到一些比较少见的报错,就会不知道这个报错的原因是什么 了。

在设计PCB的时候,为了满足各项设计要求的原因,我们需要设置很多的约束规则,然后设计完成之后,去进行DRC检查。DRC检查就是检查我们的PCB设计是否满足所设置的规则,常见的DRC检查有开路,短路,间距等等规则约束。

扫码关注

扫码关注