- 全部

- 默认排序

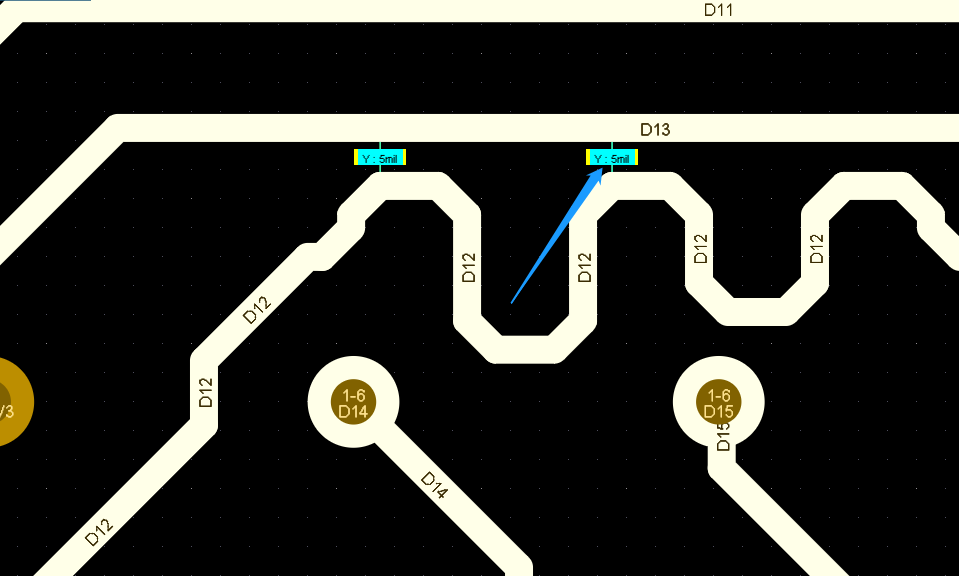

器件摆放干涉2.走线尽量不要从小器件中间穿3.数据线等长误差+-25mil,也就是50mil,后期自己重新设置一下4.地址线误差是+-50mil5.数据线等长存在误差报错地址线也存在同样的问题,后期自己绕一下蛇形等长6.数据线和地址线之间最

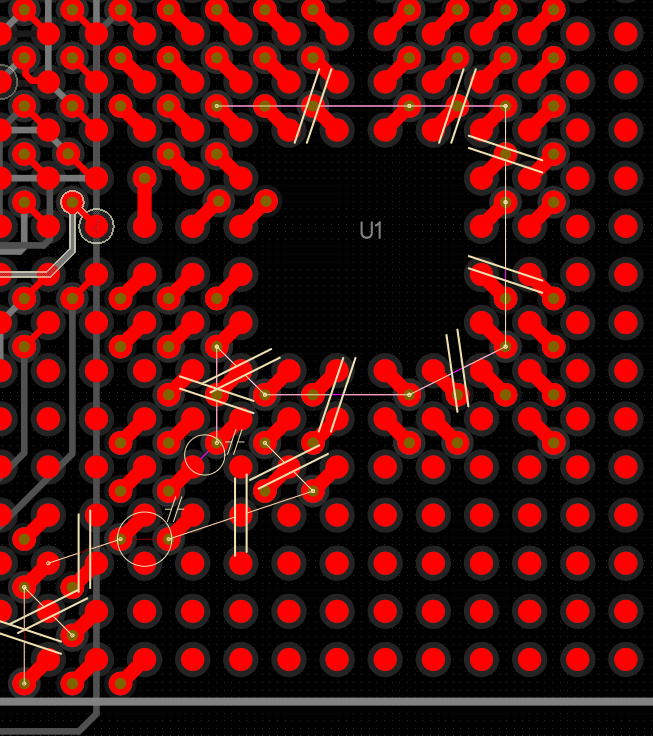

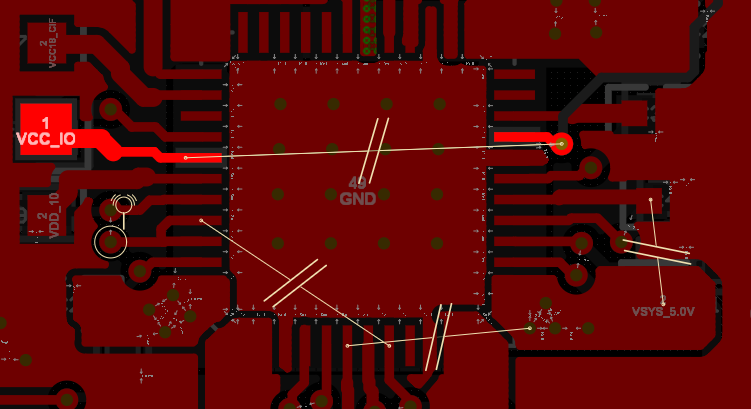

BGA内的电源并未处理,注意要么铺铜要么在电源层进行分割:注意看下U1-U16的地址控制时钟需要组内满足误差 ,还存在报错 ,重新组内等长:U16-U17的地址控制时钟注意对内的等长误差,还存在报错:数据线内也存在等长误差报错:数据线之间满

很多电子工程师会选择使用Sigrity软件进行高速PCB信号仿真,但在使用过程可能会遇见报错情况,其中之一是提示找不到电容的S参数,那么如何解决这个问题?一般来说,S参数的全称为Scatter参数,即散射参数,是在传输线两端有终端的条件下定

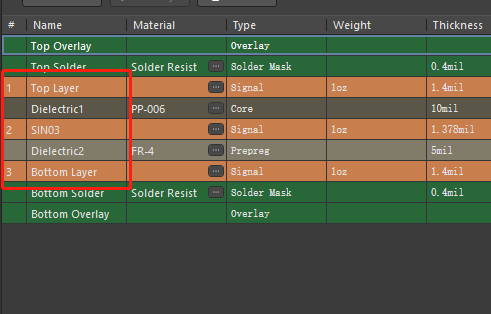

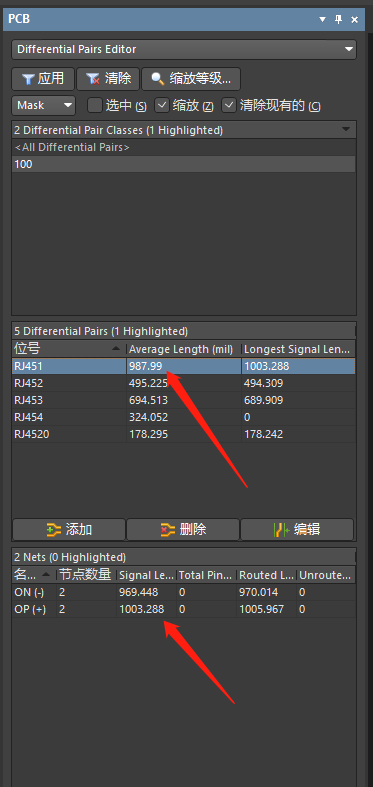

层叠一般都是双数,一般是4层,6层增加,高速信号都需要有完整的参考平面的2.差分走线注意要满足差分间距要求3.CC1和CC2属于重要信号管脚,走线需要加粗处理,ESD器件尽量靠近管脚摆放4.存在多处开路报错5.差分注意能顶层连通的就不用打孔

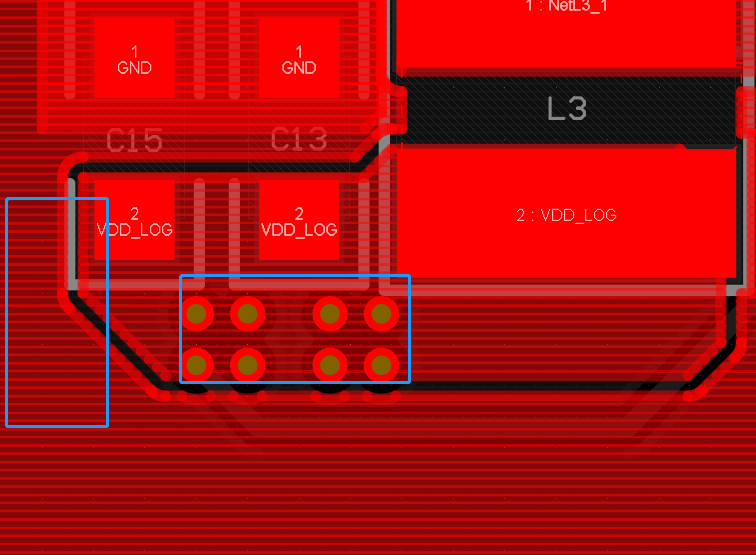

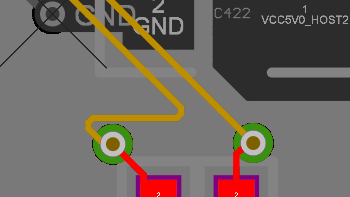

输出打孔要打在滤波电容后面2.此处不满足载流,载流是一铜皮最窄出计算的,后期自己加宽一下铜皮3.铺铜是尽量把焊盘包裹起来,这样容易造成开路4.存在多处开路和drc报错5.电感下面不要走线和放置器件6.注意中间散热焊盘上的过孔需要开窗处理7.

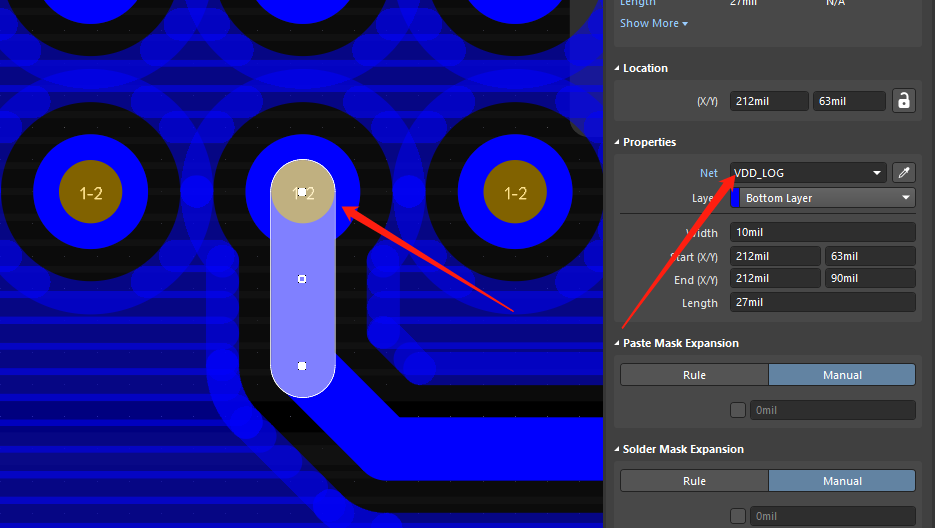

存在无网络过孔,短路了2.输出过孔要打在最后一下滤波电容的后面3.过孔不要上焊盘4.电感下面尽量不要放置器件和走线5.存在多处开路和drc报错,后期自己处理一下6.注意走线需要连接到焊盘中心,此处需要优化一下7.相同网络的走线和铜皮未进行连

还存在多处开路报错:看下此处是什么元素跟元素的间距报错:检查了对应自己修改。电感底部不要放置器件 ,净空,自己重新布局下:并且电感内部挖空处理:看下此处VCCIO线宽是否满足其载流大小:处理下多余线头删除,连接到过孔中心:走线不要出现直角:

网口差分需要进行对内等长,误差5mil2.注意差分走线要注意耦合3.注意等长线之间需要满足3W规则4.等长存在误差报错5.地网络进行就近打孔,连接到地层,缩短回流路劲6.顶层BGA里面的铜尽量挖掉7.电感所在层内部需要挖空处理以上评审报告来

注意数据线等长需要满足3W规则2.地址线之间等长也需要满足3W规则3.注意数据线扇孔线宽尽量保持一致4.地址线等长存在误差报错5.等长组创建有问题,有很多网络没有添加到里面,后期自己重新创建一下6.注意走线不要有直角和尖角,尽量钝角7.注意

扫码关注

扫码关注