- 全部

- 默认排序

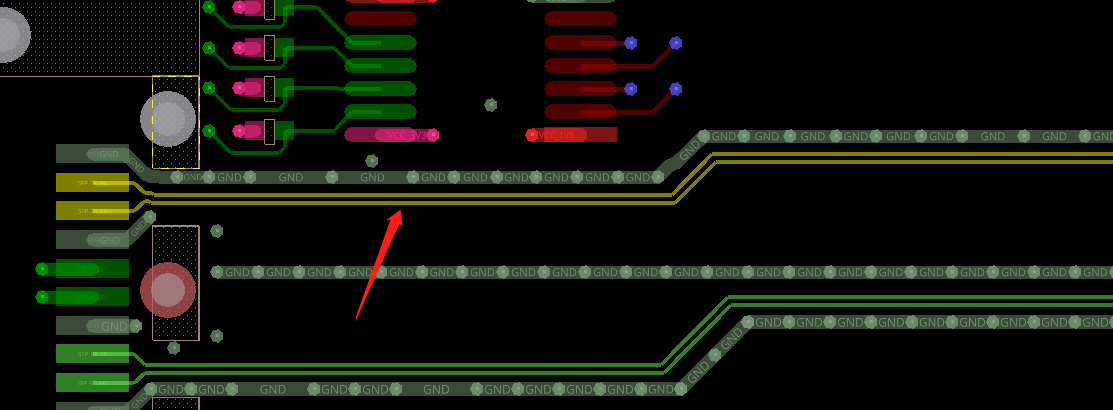

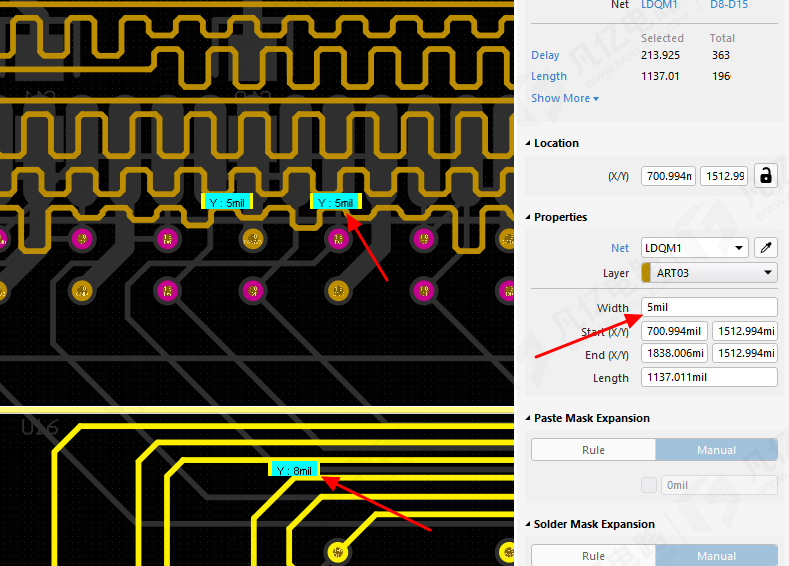

差分信号尽量包地包完全:此处上述一致原因,可以优化:此处电源信号的铜皮尽量优化宽一点,不然整体的铜皮载流量是从最窄处计算的:差分对内需要做等长处理,误差胃5MIL:此对差分没有做等长处理:其他的没什么问题。以上评审报告来源于凡亿教育90天高

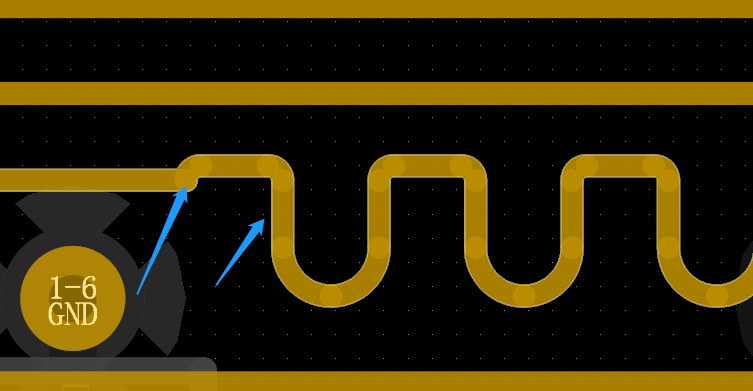

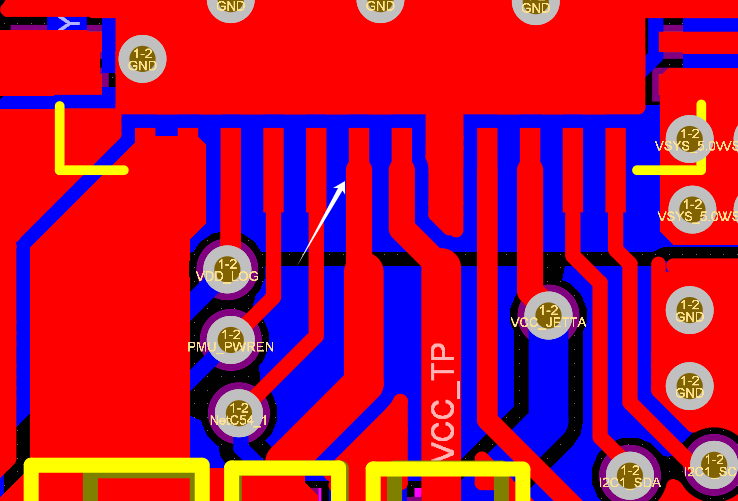

走线需要优化一下尽量钝角绕蛇形,等长可以在优化一下2过孔需要盖油处理,且里面不要有多余的线头3.注意pcb上尽量使用同一种类型的过孔,过孔种类不要超过两个4.器件摆放注意不要干涉5.走线不需要开窗,加后期自己处理一下6.还有电源为处理,存在

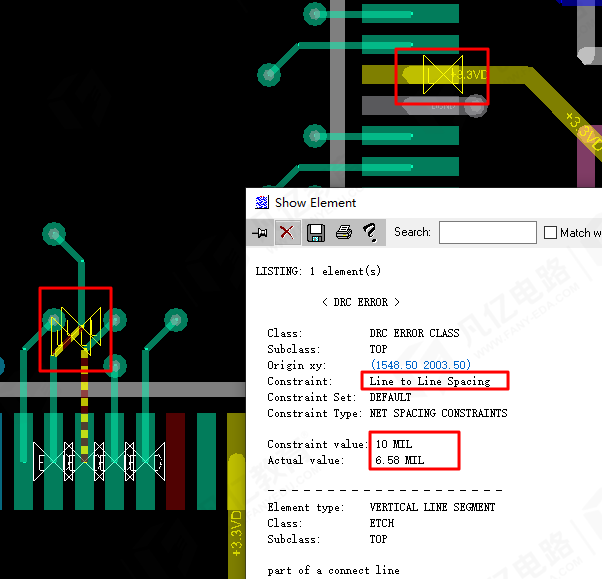

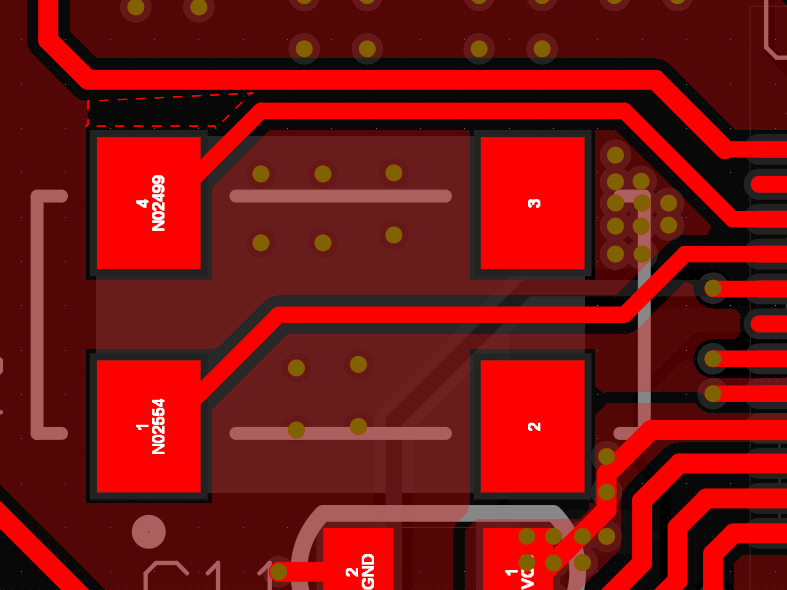

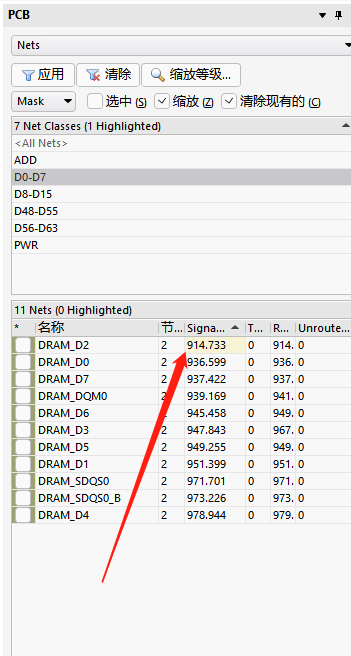

可以解决的报错处理一下顶层焊盘没有连通,器件没有连接所有等长组都没有达到等长目标以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/it

晶振注意包地:缝合孔不需要打太密集,间距150mil放置一个即可:过孔不要打在焊盘上,自己注意调整:多处存在这样的情况,自己更改。铺上铜皮就不用走线了:走线不能在器件内部:晶振是需要保持净空的,不能走线:以上评审报告来源于凡亿教育90天高速

走线保持3w间距等长绕线尽量咬合电容尽量靠近焊盘,电源走线加粗时钟线等长错误以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/item

走线在焊盘中,走线宽度不要超过焊盘,可以拉出后在加粗铺铜不要有直角电感下面不要走线以上评审报告来源于凡亿教育90天高速PCB特训班作业评审如需了解PCB特训班课程可以访问链接或扫码联系助教:https://item.taobao.com/i

如果要说全球芯片先进制程,排在第一一定是中国台湾区域,其次日韩、美国等,中国虽然半导体行业发展蓬勃,但目前是以成熟制程为主。近日,美国半导体协会(SIA)和波士顿顾问公司(BCG)联合发布数据报告,其中显示:随着美国“芯片法案”的推出,预计

随着ChatGPT的火爆,以生成式人工智能(AI)和大预言模型为主的AI行业席卷全球,各大企业组织等纷纷发展AI业务,争取拿下一席之地。近日,有研究机构发表数据报告,表示:2022年全球AI市场规模约为4541.2亿美元,2023年增至53

为了提高本国的半导体制造能力,许多国家政府及企业推出一系列政策法规,目前全球半导体制造能力最强的是欧美国家、中国台湾、日韩等。Intel CEO帕特·基辛格在近期举办的2023-2024年度企业社会责任(CSR)报告中,提出了一个宏伟的目标

等长存在误差报错2.注意地址线之间等长也需要满足3W规则3.尺寸走线需要优化一下,尽量不要走直角4.地址线等长存在误差报错后期自己调整一下时钟差分信号中高端匹配电阻应该靠近T点放置等长可以在优化一下,满足3W的前提尽量紧凑一些,提高空间利用

扫码关注

扫码关注