- 全部

- 默认排序

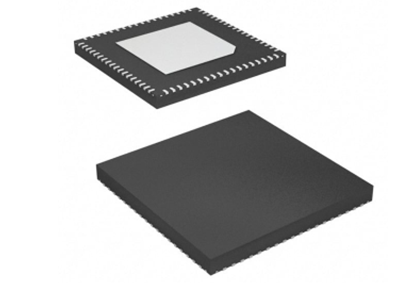

答:在进行PCB布线之前,都需要先做扇出工作,方便内层布线。对于电阻电容后者是小的IC类器件,可以直接进行手动扇出,但是对BGA类的器件,管脚数目太多,如图5-122所示,这样手工去扇出的话,工作量太大,而却BGA区间必须要扇孔在焊盘的中心位置,所以手动扇出是不现实的,这里我们讲解下,如何对BGA器件进行自动扇出,提高设计的效率,具体操作如下所示:

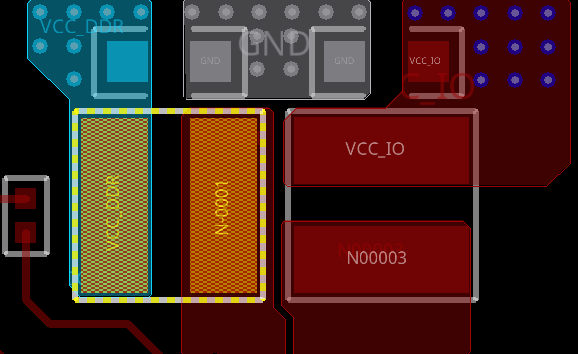

答:我们PCB布局完成之后,需要对网络进行扇出,一般空的管脚、空的网络不需要进行扇出,为了提高布线效率,我们会对空的网络进行高亮显示,具体的操作步骤如下所示:

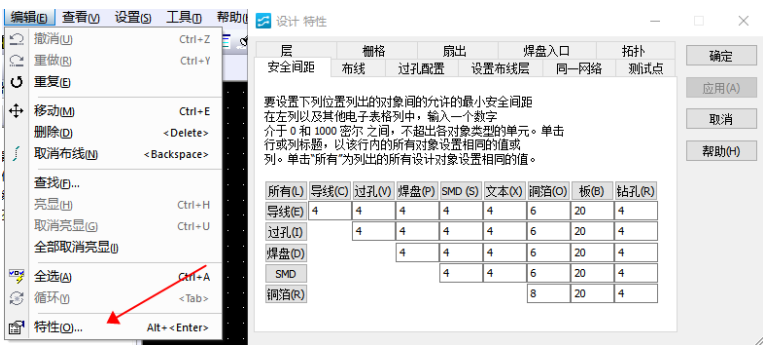

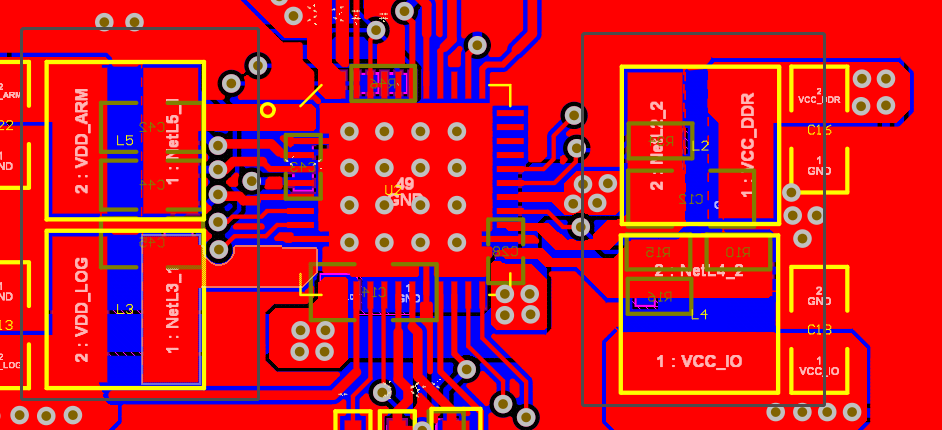

PADS Router组件内设计规则包括层、栅格、扇出、焊盘入口、拓扑、安全间距、布线、过孔配置、设置布线层、同一网络、测试点等规则。一般会对层、扇出、安全间距、布线、过孔配置、设置布线层这几项进行设置,其他项按默认选项。执行“编辑-特性”

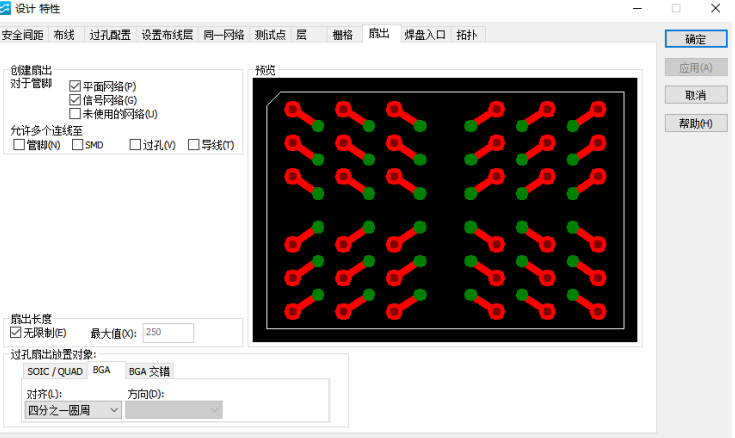

BGA扇出介绍

BGA扇出前须设置好规则,将BGA下方器件挪走,BGA下方所有层布线清除,若扇出时有DRC产生,会导致扇出失败。扇出前将格点设置为PIN间距的一半或者0,设置为PIN间距一半时须将精度设置好,否则会导到设置的格点4舍5入,设置失败。选择好合

概述1、ADCLK846BCPZ 是一个1.2GHz LVDS/CMOS,扇出缓冲区优化的低抖动和低功耗操作。可能的配置范围从6 LVDS到12 CMOS输出,包括LVDS和CMOS输出的组合。两条控制线用于确定输出的固定块是LVDS还是

单击一般工具栏中的布线图标,调出布线工具栏 从左到右依次为布线、扇出、优化、调整、居中。布线:布线指令会将所选取的对象进行交互式自动布线设计扇出:自动针对所选取的SMT元件、单个管脚或网络做扇出布线,并按照设定的规 则进行分析布线优化:

电感当前层的内部挖空处理:上述一致问题:注意不同地之间至少满足2MM间距:变压器信号除了差分信号,其他加粗20MIL走线:注意差分对内等长的GAP大于等于3W:焊盘扇孔注意对齐扇出:注意等长线之间满足3W间距原则可以调整下:注意的过孔之间的

注意电感当前层的内部铜皮挖空:焊盘扇孔注意下对齐扇出:上述一致问题,优化下电感内部的挖空区域:个别信号没有联通:其他的没什么问题。

电感底部不能放置器件,建议吧电阻电容放到IC底部去,重新布局下:铺铜尽量不要直角以及尖角:类似情况的都自己修改下。电感内部要挖干净:扇孔要对齐等间距:板上这种死铜去除掉:铜皮都仔细认真绘制,把焊盘包裹上,不要很随意:焊盘扇出主意拉直出去,跟

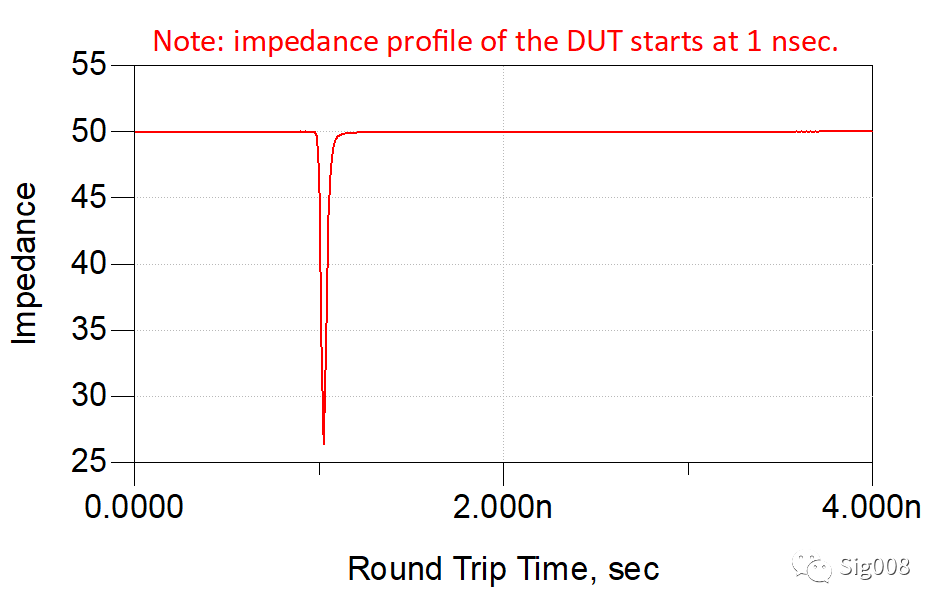

单从焊盘这一点来看,可以看到阻抗一般会比较小,但是对信号未必造成比较大的影响,可问题就在于,整个链路的阻抗不连续点不止这一处;比如,信号BGA处的焊盘,扇出孔,连接器等都是阻抗不连续处,那么这些地方和电容的焊盘就会互相影响,我们来看S参数:可以看到,红色为仅有电容焊盘时的反射,在与扇出孔级联后会变得

扫码关注

扫码关注