- 全部

- 默认排序

串行总线的发展一共目前可以总结分为3个环节时期, 时钟并行总线:小于200MHZ,比如CPCI,PCIX,SDRAM,ISA,PIC 源同步时钟并行总线:小于3200Mbps,比如DDRr1234系列,MII,EMMC 高速串行总线:最高有56NRZ ,比如USB1/2/3/3.1/3.2,PCIE3,PCIE4,SAS3,SAS4.

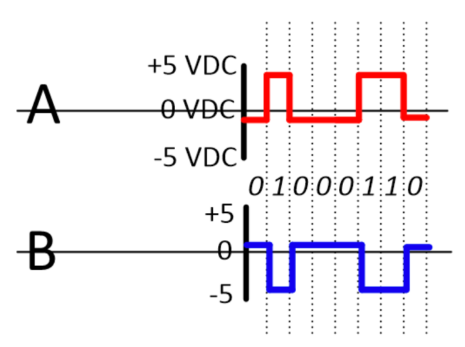

RS485作为常见的总线之一,几乎每个工控设备都在用,我们也对其熟悉不过了。我们都知道RS485双半双工通信,其CPU内部的根源是串口通信,串口通信是区分发送TX和接收RX的,在同一对差分信号线上同时传输TX、RX,就是进行方向的控制,方向的控制时机不对,数据传送是要出问题的。

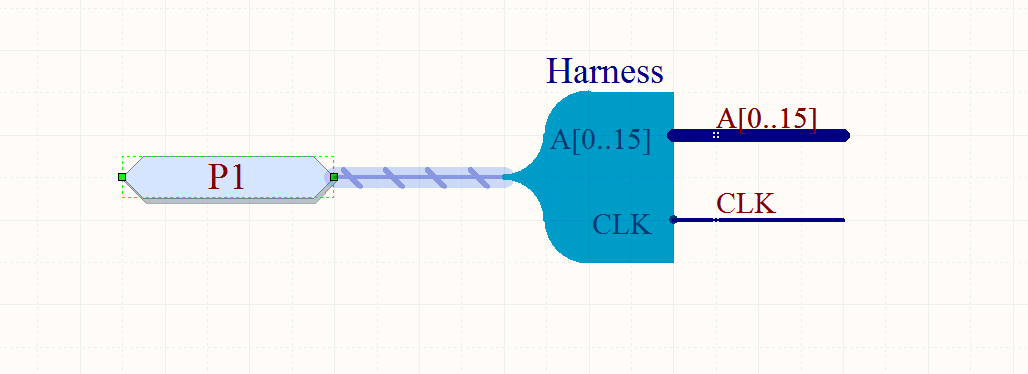

简化原理图线束的使用方法

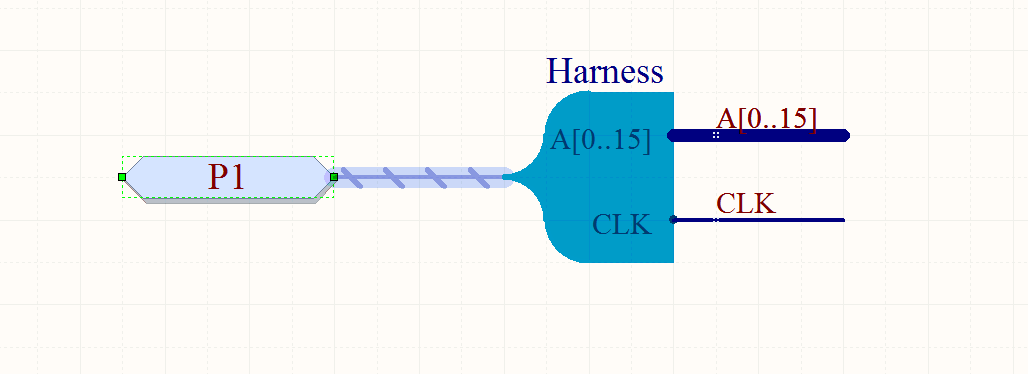

自Altium Designer6.8之后的版本引入了信号线束(Signal Harnesses)这个概念,并增加了放置、连接功能。信号线束主要用于原理图中连接不同的信号,可以把单条走线和总线汇集在一起并连接到其它信号线束上,这样能简化原理图设计,增强了设计的灵活性和流线性。

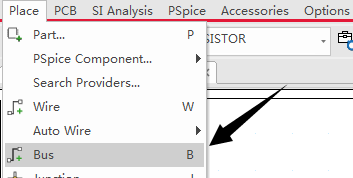

总线由总线,总线分支及网络标号组成,代表具有相同电气特性的一组导线,在具有相同电气特性的导线数目较多的情况下,可采用总线的方式,以方便识图,这里就讲解下如何放置总线及总线分支。

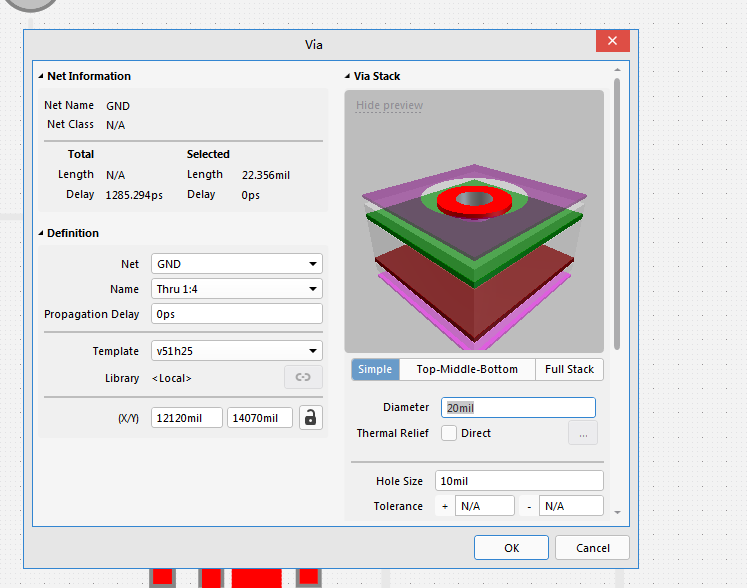

有时候为了为了增大内层的敷铜面积,特别是BGA区域,尤其在高速串行总线日益广泛的今天,无论是PCIE,SATA串行总线,还是GTX,XAUI,SRIO等串行总线,都需要考虑走线的阻抗连续性及损耗控制,而对于阻抗控制,主要是通过减少走线及过孔中的STUB效应对内层过孔进行削盘处理。

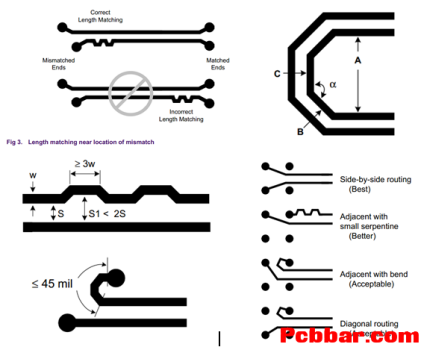

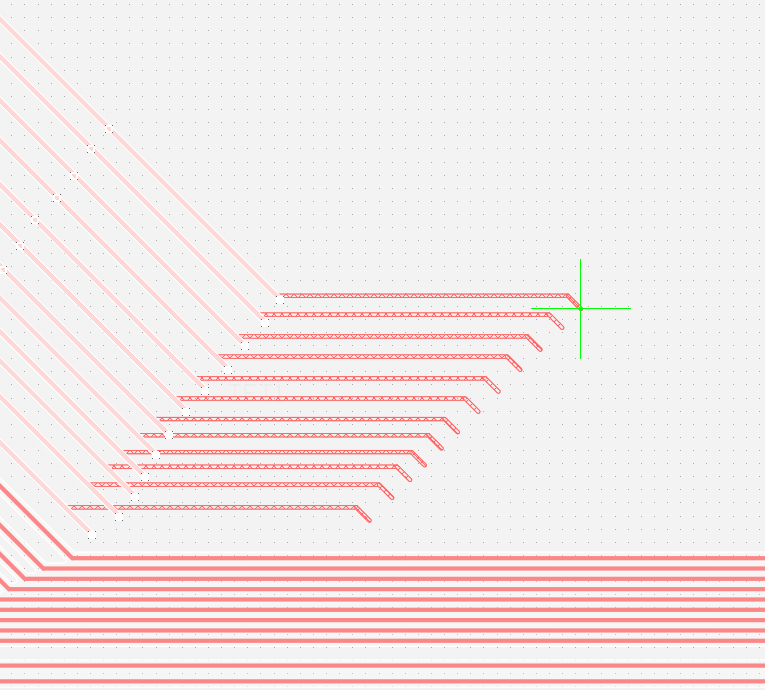

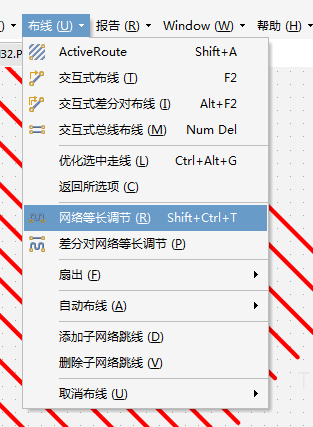

在PCB设计中,蛇形等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多条数据信号基于同一个时钟采样,每个时钟周期可能要采样两次甚至4次,而随着芯片运行频率的提高,信号传输延迟对时序影响比重越来越大,为了保证在数据采样点能正确采集所有信号的值,就必须对信号传输延迟进行控制。

至于USB,SATA,PCIE等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方时钟包含在数据中发出,数据接收方通过接受到的数据恢复出时钟信号。这类串行总线没有上述并行总线等长布线的概念。但因为这些串行信号都采用差分信号,为了保证差分信号的信号质量,对差分信号对的布线一般会要求等长且按总线规范的要求进行阻抗匹配的控制

自Altium Designer6.8之后的版本引入了信号线束(Signal Harnesses)这个概念,并增加了放置、连接功能。信号线束主要用于原理图中连接不同的信号,可以把单条走线和总线汇集在一起并连接到其它信号线束上,这样能简化原理图设计,增强了设计的灵活性和流线性

扫码关注

扫码关注