- 全部

- 默认排序

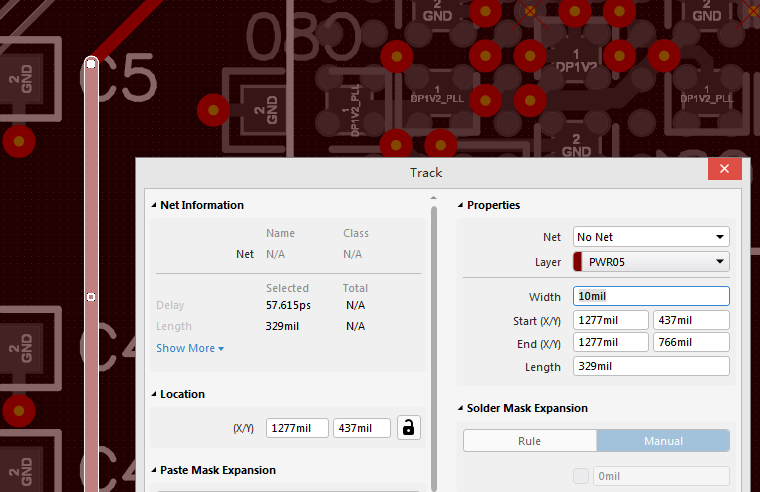

建议平面层的分割带宽度至少20MIL:地址信号类的等长还存在个别信号的误差报错:误差报错的信号自己再去等长优化。建议地址跟数据线两个类之间的信号可以走一根GND信号线进行分割开:或者自己预留20MIL的宽度。整个电源平面的信号都是3.3V信

信号传输的速率越来越高,对网络带宽的需求越来越高,高速高频电路逐渐替代低速电路成为主流。可以说,现在是属于高速数字的世界,未来将需要大量的懂高速电路设计的人才。高速电路的核心是信号完整性,学信号完整性,必然也有信号仿真,信号仿真是很多电子工

Avant-X —— 高速中端FPGA简介Avant-X FPGA系列基于Avant平台构建,为通信、计算、工业和汽车市场的中端应用提供低功耗、先进的互连和优化的计算能力。Avant-X高级互连FPGA旨在实现高带宽和安全性,其功能集可根据

Avant-X:高速中端FPGAAvant-X™ FPGA系列基于Lattice Avant平台构建,为通信、计算、工业和汽车市场的中端应用提供低功耗、先进的互连和优化的计算能力。Avant-X器件提供最高1 T/s的总系统带宽、带硬核DM

Virtex UltraScale 产品优势Virtex™ UltraScale™ 器件在 20nm 提供最佳性能与集成,包含串行 I/O 带宽和逻辑容量。作为在 20nm 工艺节点的业界仅有高端 FPGA,此系列适合从 400G 网络到大

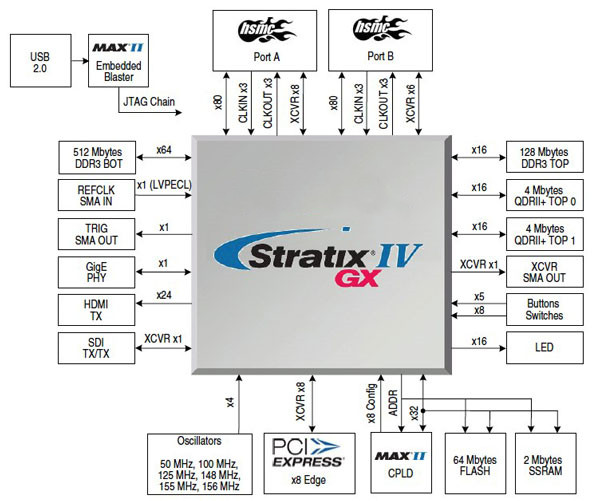

芯片概述Stratix® IV 高密度、高性能 FPGA 具有前所未有的系统带宽和功率效率,适用于高端应用,您可借其实现彻底地创新。Stratix IV 系列器件共有三种优化型号,可满足不同的应用需求。Stratix IV E (增强型)

第三代半导体材料是指以氮化镓(GaN)和碳化硅(SiC)等为代表的宽禁带半导体材料。具体是指Eg(带隙宽度)≥2.3eV的宽禁带半导体材料,主要包括碳化硅(SiC)和氮化镓(GaN)。与前两代半导体材料相比,第三代半导体材料具有更宽的禁带宽

Stratix V FPGA:为带宽而打造Stratix V FPGA系列采用TSMC 28nm高性能(HP)工艺进行制造,提供110万逻辑单元(LE)、53-Mbits嵌入式存储器、3,680个18x18乘法器,以及工作在业界最高速率28

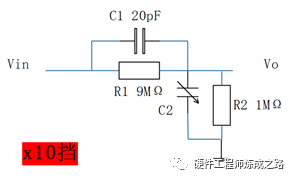

上期文章给自己挖的坑,提了一个自己当时也没整明白的问题,本没打算有后文的。结果有个小伙伴给打赏了支持,并表示想看后续,万恶的金钱啊,于是乎便有了此文。 先复盘下上期末尾的问题:X1档像X10档那样并联一个电容进行补偿来做更高的带宽到底行不行?上期举例在R1=200Ω,R2=1MΩ,C2=100pf时

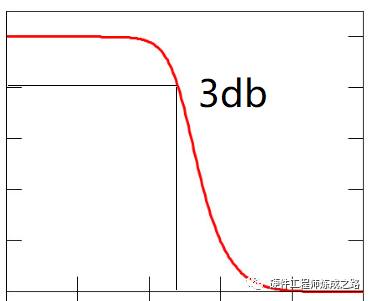

上期说到了换示波器探头,第一次使用需要对探头进行补偿电容的调节。使用示波器还有一个重要的点需要知道,那就是测试高频的时候需要用x10档,而不要用x1挡。这一点可能很多人都知道,但并不一定知道更深一点的原因,那么,我们就来说一说。 无缘高阻示波器探头带宽提一下,示波器探头的带宽也类似一个通滤波器,一般

扫码关注

扫码关注