- 全部

- 默认排序

今天看了一个工程实践EMC关于共模信号电流流向的原理及案例讲解,受益颇深,其中讲到连接器的布局和选型也是关键的一环,PCB工作地和EMC实验时的参考地之间的耦合电容的大小。有关连接器的EMC问题,下面的12个问题如果了解清楚,对自己肯定帮助很大,这是一个连接器研讨会的问题,没有给出答案,如果有连接器

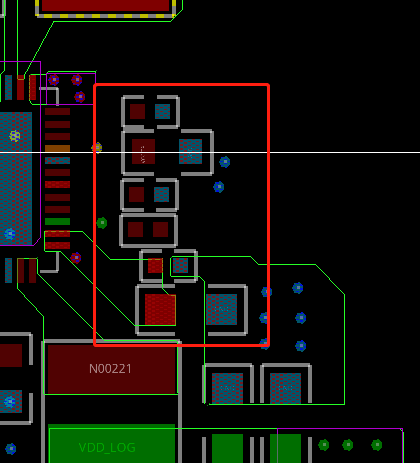

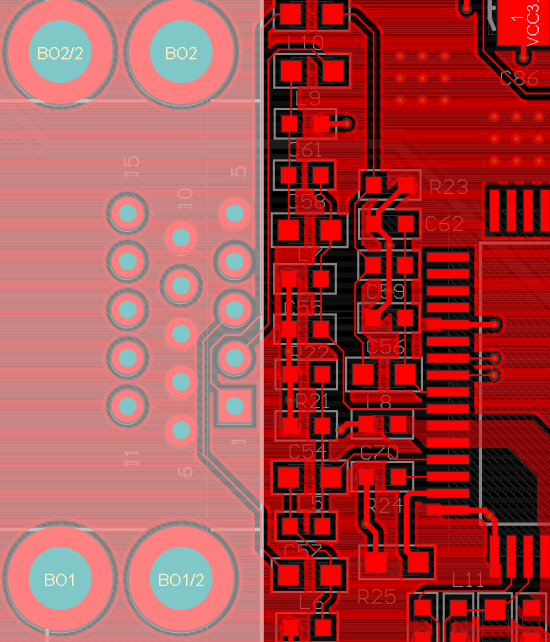

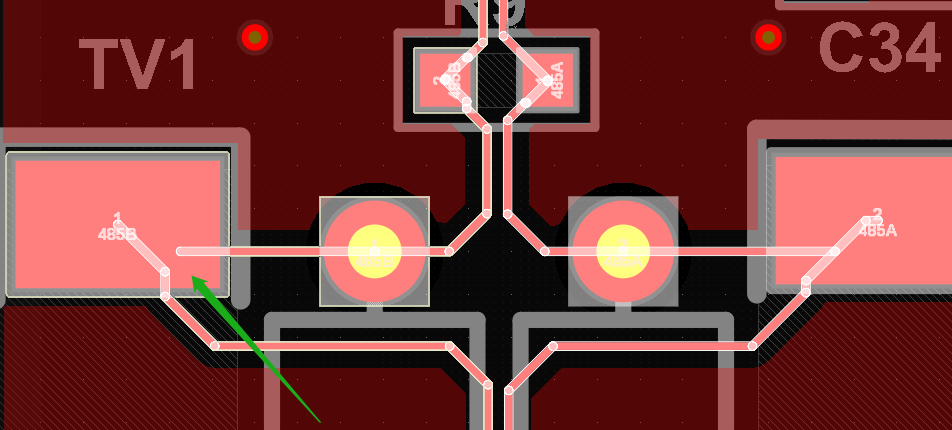

电感底部不能放置器件,建议自己优化下布局放置到IC芯片底部,自己修改下:器件尽量对齐:注意铜皮不要直接绘制,尽量钝角优化下:尽量能一块铺完的就一块,不要两块叠加,并且铜皮绘制尽量均匀,不要直角尖角:电感中间放置了铜皮挖空区域,铜皮重新灌下,

注意布局的时候器件整体中心对齐:底层器件也注意对齐:打孔也需要对齐:5V电源走线加粗或者铺铜连接好:铺铜连接之后不需要再走线连接了:注意电感内部当前层需要挖空,放置一个keepout区域:过孔都没有对齐等间距:LDO电路的电源信号也需要加粗

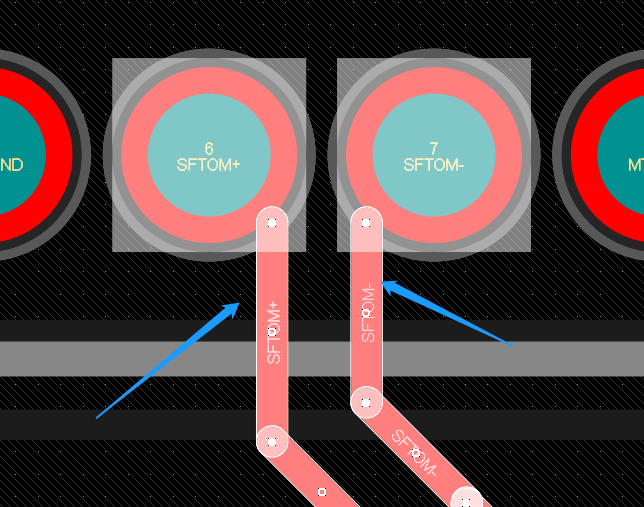

走线尽量从焊盘中心出线,避免造成开路2.差分出线要尽量耦合3.注意布局需要满足原理图规范4.注意确认此处是否满足载流5.电容尽量一个管脚一个,靠近摆放6.走线尽量不要从小器件中心穿,后期容易造成短路7.晶振尽量包地处理8.存在多处开路过孔不

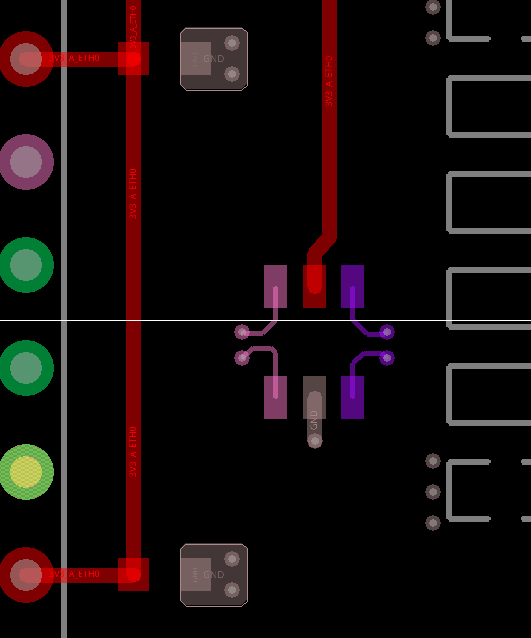

器件能放在顶层的尽量放在顶层:器件位置摆放是否有问题,需要放置完成,然后该走差分的就差分走线:接口到变压器这里的信号以及布局完全不合格,需要走差分的没有按照差分布线,查看清楚原理图,那些信号走差分 ,那些信号单端,并且差分信号拉完之后还需要

PCB覆铜是什么?如何更好覆铜?有哪些方法可以提高覆铜效率?等等,这些问题几乎是很多电子工程师在PCB设计中会遇到的问题,为更好帮助工程师成长,更好覆铜,所以下面将分享10条覆铜方法及技巧,希望对小伙伴们有所帮助。1、对不同地的单点连接,最

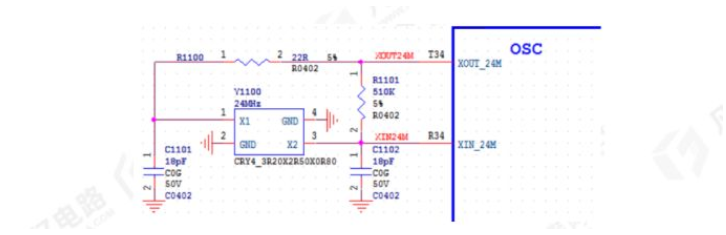

时钟电路就是类似像时钟一样准确运动的震荡电路,任何工作都是依照时间顺序,那么产生这个时间的电路就是时钟电路,时钟电路一般是由晶体振荡器、晶振、控制芯片以及匹配电容组成,如图1所示。图1 时钟电路针对时钟电路PCB设计有以下注意事项:1、晶体

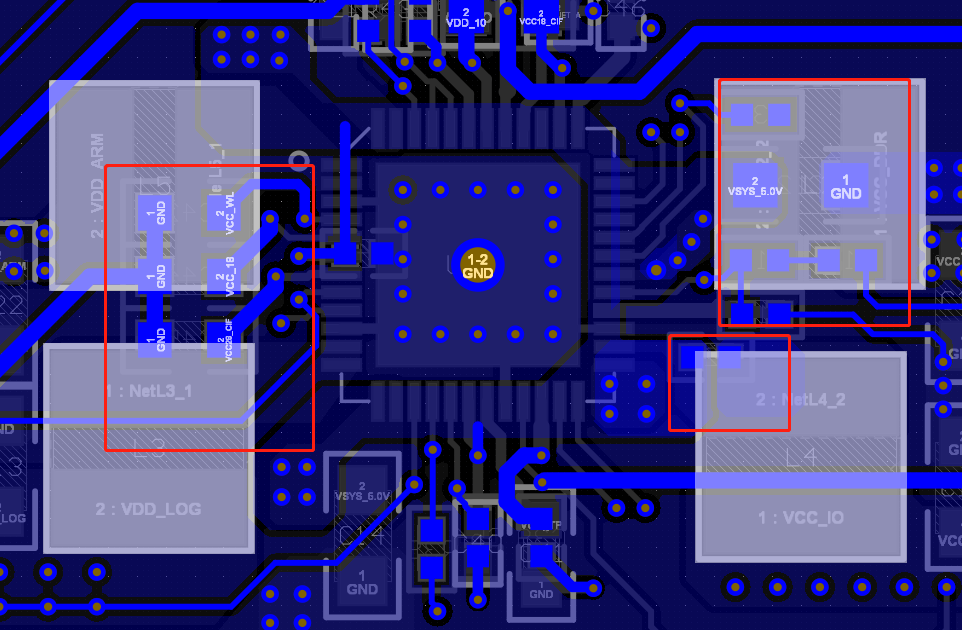

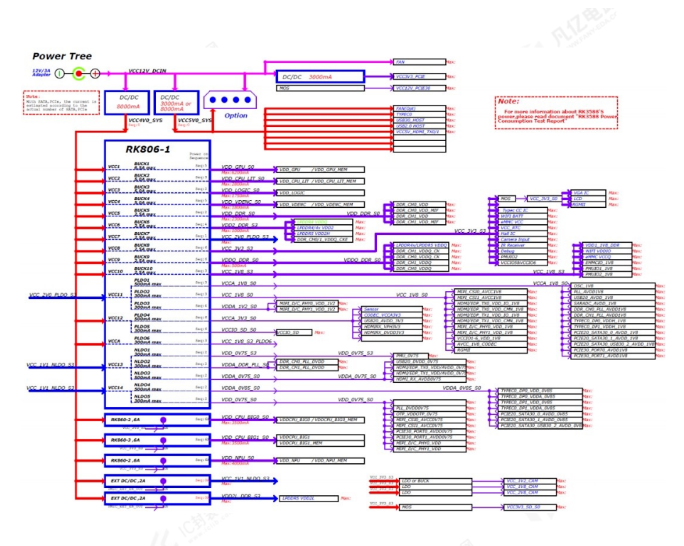

RK3588系统采用PMIC芯片RK806来进行整体供电,如图1所示。整体布局时在满足结构和特殊器件的布局同时RK806尽量靠近RK3588,如需要考虑散热设计,可以适当保持间距不要太靠近也不能离的太远,摆放方向时,尽量优先考虑 RK806

VGA模拟信号要一字型布局,走线加粗处理2.晶振需要走内差分,走线要尽量短,晶振尽量顶层走线,包地要包完整3.差分对内等长不能超过线距的两倍,包地要在地线上打孔4.跨接器件旁边需要多打地过孔,器件摆放可以在优化一下5.反馈需要从最后一个电容

走线并未完全连接,要连接到焊盘中心:注意铜皮尽量钝角,不要直角:铺了铜皮连接,里面就不用走线了:注意电源模块对应的GND过孔也是打在最后一个输出电容的管脚后面:注意下布局,电源模块布局走线优先于主干道,布局布线优先级最高,路径尽量短:电感内

扫码关注

扫码关注