- 全部

- 默认排序

在设计PCB时,经常会遇到高速差分线,比如USB、HDMI、LVDS、以太网等等,高速差分线不仅要求信号线的正端和负端信号线宽及线间距保持一致,还需要对差分信号线进行阻抗控制。控制差分信号线的阻抗,对高速数字信号的完整性是非常重要的,因为差分阻抗影响差分信号的眼图、信号带宽、信号抖动和信号线上的干扰

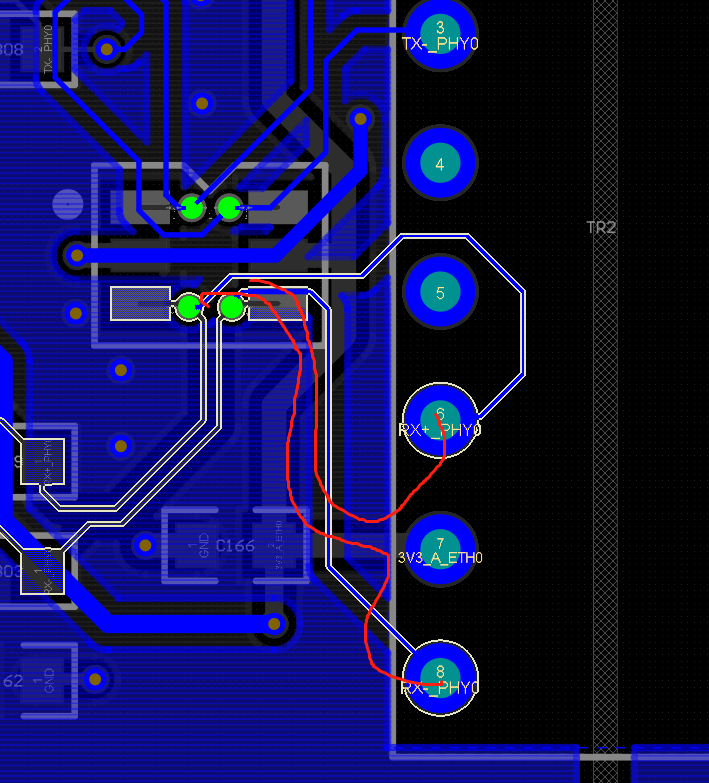

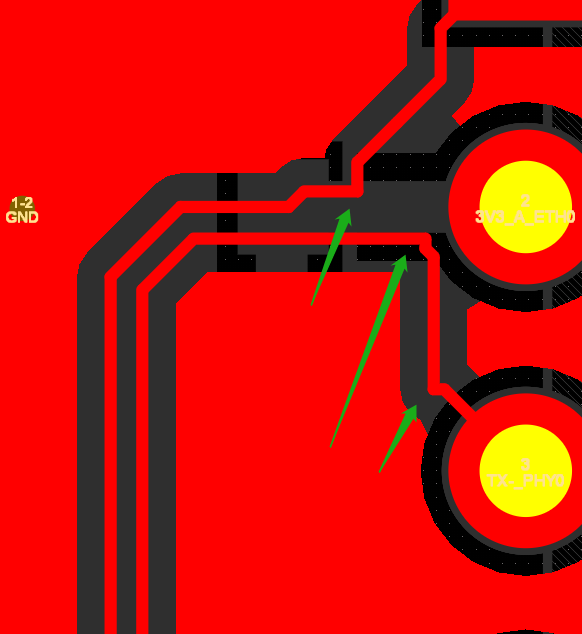

差分线要按阻抗线宽线距要求耦合走线网口到芯片的差分都需要优化,后期自己好好理解差分,然后走线需要调整一下2.器件摆放尽量中心对齐处理3.走线需要优化一下,不要有锐角4.TX分组错误5.注意等长蛇形走线尽量45度,不要直角6.除了散热过孔,其

差分线都不合格,都存在直角:完全是不允许的,需要删除重新走线。上面那组差分出现,需要跟下面那组一样,下面的差分是完全合格的耦合走线:焊盘不能随意出现,需要从中心往两长边拉线:差分对内等长误差为5MIL:单端线等长改下等长模式,也是不能直角:

差分线对内等长误差5mil,同一组差分误差5mil规则要分开进行设置,后期自己处理一下2.焊盘出线不要走直角3.差分对内等长尽量在不耦合处进行等长4.注意器件摆放不要超出板框5.差分走线要耦合走,后期自己优化一下6.后期自己在地平面铺铜,把

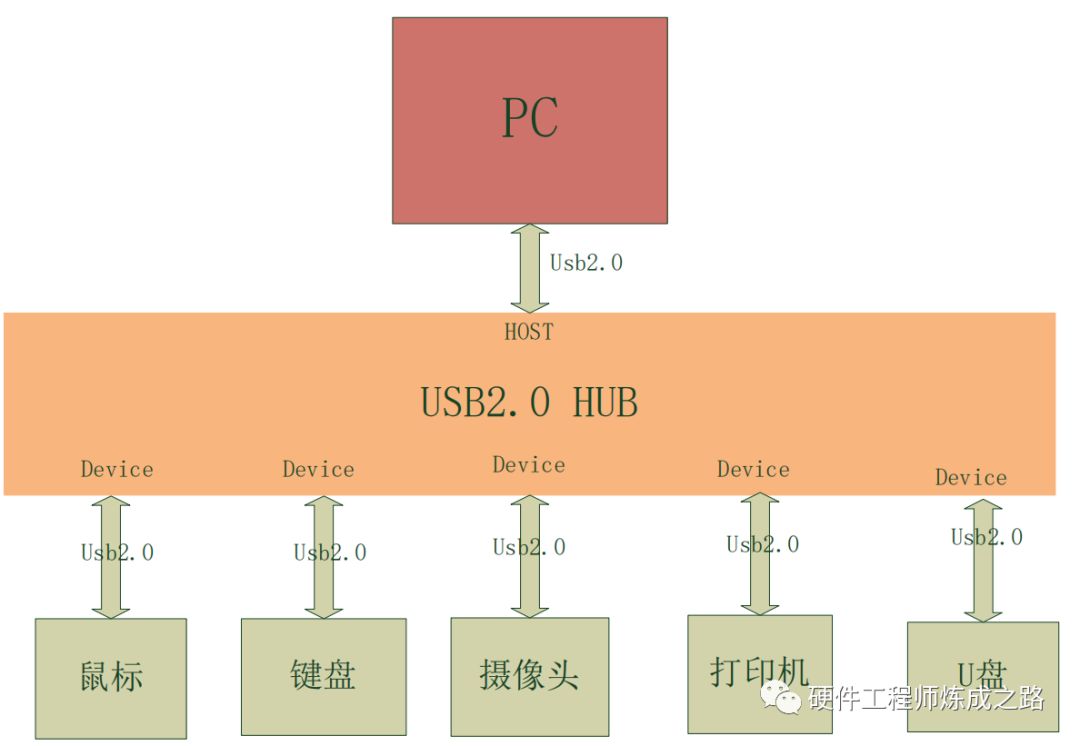

USB2.0规范中传输速度是480 Mbps(即60 MB/s)。但是很多USB2.0设备在实际工作时的数据传输速度却与此相差甚远,比如用PC用U盘拷个东西,往往比60MB/s慢很多,这是为什么呢?其实想想也能知道一些原因,USB总线中传输数据的就一对差分线,单是其要同时支持各种设备(一个USB H

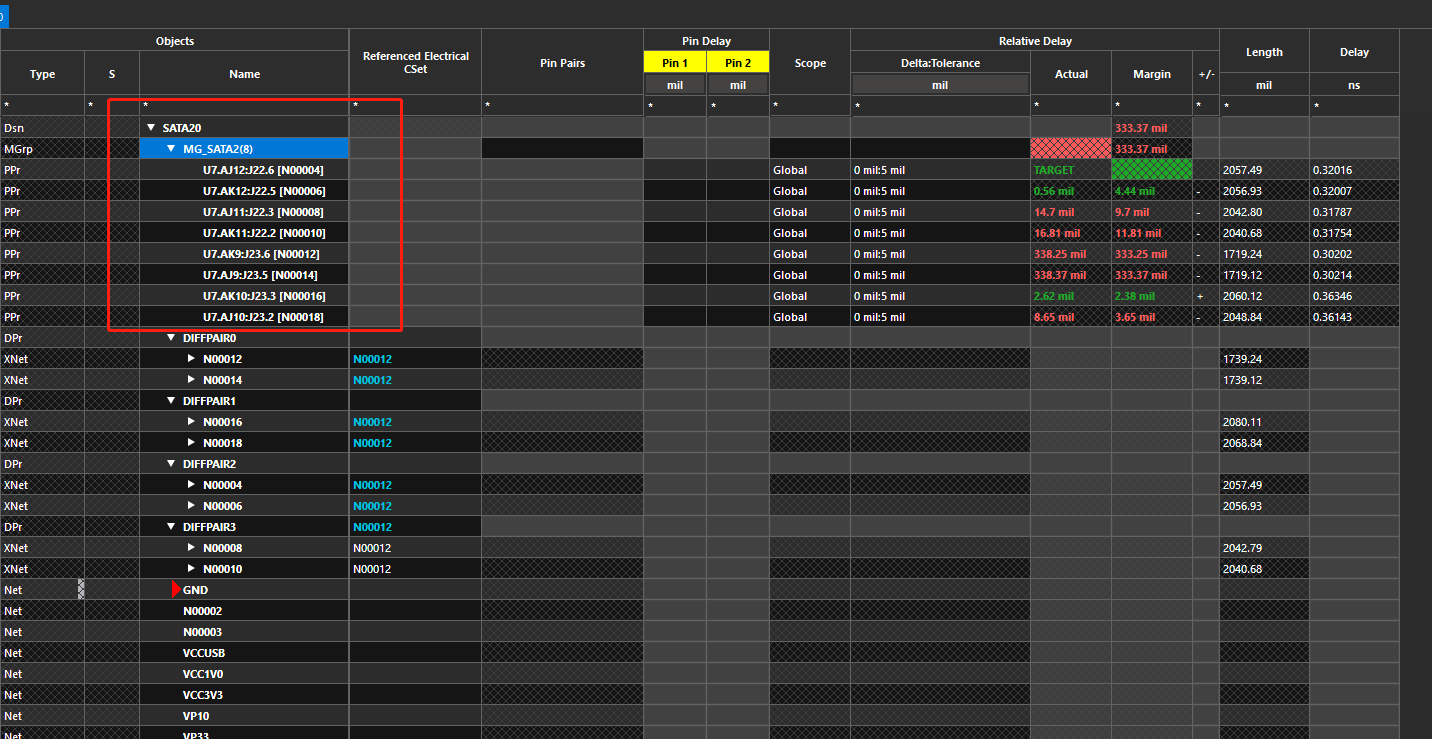

差分走线等长调节

最近在画板子很多USB接口,都是差分线,差分线会走,在AD里面快捷键P+I就可以走差分线了,但是差分线两端直接走线过去的长度可能需要绕一下才能达到另一端。问题1:如果一对差分线,其中一条需要绕一下才能和另一条等长,那么怎么只绕其中一条,而另一条不饶呢?问题2:以前的差分线都是直接走常规线,一条一条的

扫码关注

扫码关注